# A survey on run-time power monitors at the edge

DAVIDE ZONI\*, Politecnico di Milano, Italy ANDREA GALIMBERTI, Politecnico di Milano, Italy WILLIAM FORNACIARI, Politecnico di Milano, Italy

Effectively managing energy and power consumption is crucial to the success of the design of any computing system, helping mitigate the efficiency obstacles given by the downsizing of the systems while also being a valuable step towards achieving green and sustainable computing. The quality of energy and power management is strongly affected by the prompt availability of reliable and accurate information regarding the power consumption for the different parts composing the target monitored system. At the same time, effective energy and power management are even more critical within the field of devices at the edge, which exponentially proliferated within the past decade with the digital revolution brought by the Internet of things. This manuscript aims to provide a comprehensive conceptual framework to classify the different approaches to implementing run-time power monitors for edge devices that appeared in literature, leading the reader toward the solutions that best fit their application needs and the requirements and constraints of their target computing platforms. Run-time power monitors at the edge are analyzed according to both the power modeling and monitoring implementation aspects, identifying specific quality metrics for both in order to create a consistent and detailed taxonomy that encompasses the vast existing literature and provides a sound reference to the interested reader.

CCS Concepts: • Hardware  $\rightarrow$  Power estimation and optimization; • Computer systems organization  $\rightarrow$  Embedded systems; • General and reference  $\rightarrow$  Surveys and overviews.

Additional Key Words and Phrases: Power modeling, power monitoring, power management, run-time, run-time power modeling, run-time power monitoring, run-time power management, edge computing, survey

# **ACM Reference Format:**

Davide Zoni, Andrea Galimberti, and William Fornaciari. 2023. A survey on run-time power monitors at the edge. *ACM Comput. Surv.* 1, 1, Article 1 (January 2023), 33 pages. https://doi.org/10.1145/3593044

#### 1 INTRODUCTION

Edge computing brings data storage and processing at the edge of the network, i.e., physically closer to users, drastically reducing the communication bandwidth and latency and avoiding the need to send information which might be private, sensitive, or safety-critical [95, 98]. The edge computing paradigm mitigates therefore the concerns typical of cloud computing about the inefficient usage of costly, centralized resources, their environmental impact, and the privacy risks posed by storing users' data in remote places [5, 68]. Edge gadgets can often be battery-powered mobile devices or even resort to energy-harvesting solutions, and in general it is crucial to deal with their energy and power constraints. At the same time, as the applications and services they provide vary in complexity, edge gadgets comprise a wide and heterogeneous range of devices with different processing capabilities [50].

Authors' addresses: Davide Zoni, davide.zoni@polimi.it, Politecnico di Milano, P.zza L. Da Vinci, Milano, Italy, 20133; Andrea Galimberti, andrea.galimberti@polimi.it, Politecnico di Milano, P.zza L. Da Vinci, Milano, Italy, 20133; William Fornaciari, william.fornaciari@polimi.it, Politecnico di Milano, P.zza L. Da Vinci, Milano, Italy, 20133.

<sup>\*</sup>Corresponding and leading author

<sup>© 2023</sup> Copyright held by the owner/author(s). Publication rights licensed to ACM.

This is the author's version of the work. It is posted here for your personal use. Not for redistribution. The definitive Version of Record was published in *ACM Computing Surveys*, https://doi.org/10.1145/3593044.

The processing components of devices at the edge are in charge of efficiently performing a large variety of computation- and communication-intensive tasks within tight energy constraints [21], and satisfying the energy- and power-efficiency requirements is a key aspect of their design for two main reasons. On the one hand, the ever-stricter time-to-market constraints, that impose to accommodate a large variety of application scenarios, have been driving the design of over-provisioned computing platforms, causing a significant fraction of the available computing resources to be left unused in real-world scenarios. On the other hand, the requirements for newer and more complex heterogeneous applications impose pairing multi-core processors with specialized hardware accelerators, thus making the overall computing platform even more complex and difficult to optimize.

To this end, run-time optimization techniques and the related monitoring infrastructures are foreseen as the solution to optimize the energy efficiency of modern computing platforms. Indeed, the effectiveness of any run-time energy optimization technique is strongly related to the quality of the measurements or estimates of power consumption provided by a run-time power monitoring system. The latter leverages either a direct measurement strategy or an indirect estimation one. Direct methods ensure high accuracy at the cost of poor scalability, due to the need to adopt a mixed analog-digital design, and high implementation costs. Indirect methods leverage the correlation between the power consumption and a carefully selected set of the platform's run-time statistics to deliver periodic power estimates. In general, indirect methods are more scalable and cheaper due to the possibility of selecting the platform's statistics to design the power monitor at different level of abstractions, i.e., ranging from the architectural performance monitoring counters down to the switching activity of the microarchitecture.

Notably, the usage of run-time power monitors has been extensively studied within the scenarios of high performance computing (HPC) [82] and datacenters [54, 65], while several state-of-the-art contributions specifically target the design of run-time power monitors for high-performance CPUs [69] and GPUs [13]. These surveys highlighted the complex taxonomy in the fields of power monitoring systems for HPC as well as for high-performance CPUs and GPUs, while, in contrast, the large amount of work targeting run-time power monitors at the edge is still unstructured and is missing a comprehensive taxonomy. The ever-increasing needs to ease the design of effective monitoring systems and to better identify the areas that require further research make it paramount to deliver a complete and comprehensive classification of the current state-of-the-art solutions in the field of run-time power monitors at the edge.

Contributions. This manuscript provides a comprehensive taxonomy of the solutions proposed in the literature of run-time power monitors targeting the processing elements of edge devices, with the final goal of helping the reader select and implement the proper infrastructure fitting the computing platform at hand as well as the system and application requirements.

The manuscript is organized according to three key principles to maximize its readability. First, each analyzed run-time power monitor is explored in terms of both the power modeling and power monitoring aspects, discussing its quality metrics for each aspect and how they correlate to each other to produce the actual implementation. Second, the proposed run-time power monitor classification considers both software- and hardware-implemented monitoring solutions that target edge computing platforms, dividing the latter into three classes, i.e., CPUs, GPUs, and hardware accelerators. Hardware accelerators can be either human-designed or generated through high-level synthesis (HLS). Third, the analyzed power monitors are evaluated in terms of functional and non-functional requirements. Functional requirements include the quality of the estimate and the temporal resolution, while non-functional ones comprise the performance, area, and power overheads due to the addition of the monitoring infrastructure.

Structure of the manuscript. The rest of this survey is organized into five parts. Section 2 introduces the theoretical background of power consumption and the core principles guiding its reduction. Section 3 overviews the state-of-the-art proposals, while a detailed discussion on power modeling and monitoring aspects is provided in Section 4 and Section 5, respectively. Section 6 draws some concluding remarks draws some concluding remarks discussing this survey's key findings and highlighting future research directions in the field.

#### 2 BACKGROUND

This section overviews the background on run-time power and energy management by giving definitions for energy and power consumption, highlighting the factors that impact the latter, and introducing the general structure of a run-time power and energy management framework, as well as the concepts of run-time power modeling and monitoring.

## 2.1 Power consumption in CMOS devices

The energy consumption E can be defined as the total amount of electricity used to perform some work by a computing platform over a specific period T. Differently, the power consumption P can be defined as the rate at which a system consumes electricity. The relationship between energy and power consumption can be formulated as shown in Equation (1).

$$E = \int_0^T P(t) dt \tag{1}$$

Energy consumption is indeed the integral of the power consumption over time, where power consumption P(t) refers to a specific time instant t. Equivalently, power consumption can be defined as the time derivative of energy consumption, according to Equation (2).

$$P = \frac{dE}{dt} \tag{2}$$

Estimating the energy consumption associated with a computing task requires predicting its power consumption at each instant. Without loss of generality, all models, modeling, and monitoring methods concerning both power and energy consumption can thus be referred to as power models, power modeling, and power monitoring methods, respectively. In CMOS devices, power consumption P can be split into two distinct components, dynamic and static power consumption [18, 61], as reported in Equation (3).

$$P = P_{dynamic} + P_{static} \tag{3}$$

The two power components are additive, and, generally, both need to be addressed to optimize the overall power consumption. The dynamic component of power consumption  $P_{dynamic}$  can be traced back primarily to switching power, which derives from the load capacitance charging and discharging during switches in CMOS gates [17]. During the charging phase of the CMOS gate, the output voltage swings from 0 to  $V_{DD}$ , dissipating energy taken from the power supply while, during the discharging phase, the energy stored in the load capacitance is dissipated. In both cases, some heat is generated. Switching power consumption is generally approximated as shown in Equation (4), where  $\alpha$  is the switching activity, i.e., the number of switching transitions per clock cycle,  $C_L$  is the equivalent load capacitance at the gate output,  $V_{DD}$  is the supply voltage, i.e., the voltage at which the load capacitance charges, and  $f_{clk}$  is the operating clock frequency.

$$P_{dynamic} \approx \alpha \cdot C_L \cdot V_{dd}^2 \cdot f_{clk} \tag{4}$$

In contrast, the static component  $P_{static}$  of power consumption can be traced back to the power dissipated by leakage currents, which also flow when the device is inactive. There are multiple

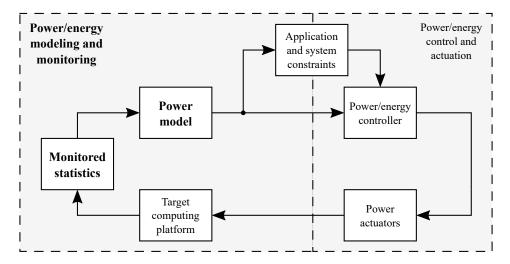

Fig. 1. Block diagram for a generic run-time power/energy management framework. This survey focuses on the blocks written in **bold**.

leakage sources, but the static power component due to the subthreshold leakage current is the most significant one, while the contribution of the others is negligible in devices that employ modern CMOS process technologies. The subthreshold leakage current derives from the transistor threshold voltage, which keeps decreasing as the node process technology advances and the transistor size shrinks. The transistor threshold voltage is reduced by design to offset the slower transistor dynamics as the supply voltage is scaled down, determining an exponential increase in the subthreshold leakage current. Static power  $P_{static}$  is approximately expressed as shown in Equation (5), where  $\beta$  and  $\gamma$  are technology-dependent constants,  $V_{dd}$  is the supply voltage,  $V_{th}$  is the threshold voltage, and  $V_T$  is the thermal voltage.

$$P_{static} \approx \beta \cdot V_{dd} \cdot e^{-\frac{V_{th}}{\gamma \cdot V_T}} \tag{5}$$

#### 2.2 Run-time energy and power management frameworks

A generic power/energy run-time management framework is composed of a set of core blocks that interact with each other in a closed-loop fashion, as depicted in Figure 1. At a coarse grain, it can be split into two main functionalities, namely *i*) power/energy modeling and monitoring and *ii*) power/energy control and actuation.

This survey will focus on the power/energy modeling and monitoring part. In particular, a power model is fed a set of select monitored statistics measured or estimated from the target computing platform. The power model and the set of monitored statistics are generally defined at design time to fit the target computing platform and provide accurate estimates at the desired temporal resolution while requiring acceptable overheads of area, performance, and power due to the monitoring infrastructure. Power modeling and power monitoring are introduced in Section 2.3, while comprehensive overviews and taxonomies are provided in Section 4 and Section 5, respectively.

On the control and actuation side, the power consumption estimates produced at run-time by the power model, together with the constraints of the running applications of the overall system, are input to the power/energy controller, which produces control signals to maintain power/energy consumption close to the desired set-points, according to the implemented policies. Finally, the

power actuators act on the target platform according to the inputs given by the power/energy controller, closing the power/energy management framework loop. Such actuators usually act on two main factors of dynamic power consumption, i.e., the supply voltage  $V_{DD}$  and the operating clock frequency  $f_{clk}$ . Actuation techniques exploited in run-time power management frameworks range from more complex dynamic voltage and frequency scaling (DVFS) [15, 44, 88, 100, 123] and dynamic frequency scaling (DFS) [64] techniques to simpler ones such as power gating [42, 46, 99, 113] and clock gating [26, 58, 117].

## 2.3 Power modeling and monitoring basics

Power modeling encompasses the design of models that can adequately estimate the power consumption of a target computing platform. A power model can generally be defined as a mathematical function that correlates the power consumption with features, measured or estimated at a certain level of abstraction, of the underlying hardware architecture. A power model can be employed mainly in two ways, i.e., as an input to either design-time power analysis or run-time power monitoring. Depending on the specific target application of a power model, it must satisfy different requirements and therefore be designed accordingly.

Design-time power analysis makes an offline use of a power model to explore the design space of the target computing platform, allowing to evaluate their energy, power, performance, and area quality metrics at an early design stage. McPAT [59], DSENT [106], ORION [49], and Strober [51] are examples of frameworks for design-time power analysis. The offline nature of power analysis carried out at an early design stage makes the performance of the underlying power model a non-critical factor. Such analysis adds no overhead in terms of performance, area, and power to the original hardware platform since it is carried out as part of the hardware design process. Notably, these frameworks often work at the architectural level and therefore employ a generic power model for multiple computing platforms, thus resulting in a low estimation accuracy [93, 118].

On the contrary, *run-time power monitoring* delivers an infrastructure to compute online estimates of the power consumption of the target computing platform. Employing them requires carefully considering the overhead in terms of performance, mainly for software implementations, and area and power, in particular for hardware implementations. In both scenarios, the run-time power monitors must be implemented in an ad-hoc manner, providing better accuracy than offline power analysis, at the cost of time spent designing the monitoring infrastructure.

# 3 RUN-TIME POWER MONITORS

This section presents the classification of the state-of-the-art run-time power monitors targeting edge devices, with the goal of providing the reader with a comprehensive overview of the available state-of-the-art contributions. In particular, Section 3.1 presents the dimensions considered for the classification, while Section 3.2 discusses the actual classification of the contributions surveyed within this manuscript. Notably, a detailed discussion of the run-time power modeling and monitoring aspects for each state-of-the-art contribution is provided in Section 4 and Section 5, respectively, while Section 6 presents the key findings as well as the future research directions.

# 3.1 Taxonomy dimensions

Each state-of-the-art proposal is classified and discussed according to four independent dimensions, i.e., target platforms, model families, power model statistics, and monitoring implementation, that are defined in the rest of this subsection.

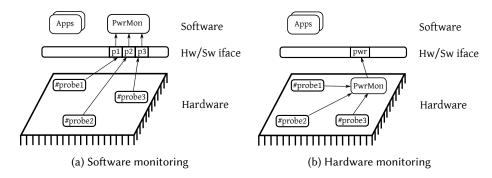

Fig. 2. Generic hardware and software implementations of run-time power monitors

- 3.1.1 Target platforms. The survey considers run-time power monitors that target the computing elements of edge devices, distinguishing between CPUs, GPUs, and hardware accelerators. General-purpose central processing units (CPU in Table 1) may be either single- or multi-core, possibly implementing multi-threading and heterogeneous architectures. Graphics processing units (GPU) accelerate highly parallel tasks and are employed in high-end embedded systems. Hardware accelerators (Accel.) provide dedicated hardware support to computationally-expensive functionalities and might be either hand-written or obtained as the output of the high-level synthesis (HLS) procedure [72].

- 3.1.2 Model families. In general, power models are either regression or machine learning models. Regression models (Regression in Table 1) are commonly used in run-time power monitoring scenarios due to their simple and low-overhead implementation. Regression may be either linear, polynomial or other more complex variants. In such regression models, power statistics are the independent variables while power consumption is the dependent one. Machine learning models (Learning in Table 1) implement the power model as a neural network, a decision tree, or a random forest.

- 3.1.3 Model statistics. Feeding the power model with optimal input statistics is of paramount importance for the sake of accuracy and effectiveness in modeling the power consumption of the target platform when considering real-world scenarios. Such input statistics can be split into two coarse-grained categories, i.e., performance events and switching activity. Performance events (Perf. events in Table 1) are commonly provided by general-purpose programmable platforms such as CPUs and GPUs through so-called performance monitoring counters (PMCs). The events collected by these counters, such as the number of instructions, branches taken, and cache misses, were initially exposed with the goal of monitoring performance in CPUs and GPUs, while their good correlation with the power consumption extended their use to power monitoring scenarios. On the other hand, the switching activity of each signal contributes to the dynamic power consumption of hardware platforms realized in CMOS technology, thus making the toggling activity (Toggl. activity in Table 1) of specific signals an alternate candidate input statistic for run-time power models. Notably, some state-of-the-art solutions also make use of additional statistics (Others in Table 1) such as voltage, frequency, and temperature measurements as inputs to the proposed run-time power models.

Table 1. Overview of the state-of-the-art contributions discussed in this survey and their classification according to the modeling and monitoring dimensions. Legend:  $\checkmark$  yes, - no; **Target** target platforms (see Section 3.1.1); **Family** model families (see Section 3.1.2); **Statistics** model statistics (see Section 3.1.3); **Implem.** monitoring implementation (see Section 3.1.4).

|       |              |              | Modeling |                       |              |              | Monitoring |                                       |              |              |

|-------|--------------|--------------|----------|-----------------------|--------------|--------------|------------|---------------------------------------|--------------|--------------|

|       | Target       |              |          | Family                |              | Statistics   |            |                                       | Implem.      |              |

|       |              |              |          |                       |              | Perf.        | Toggl.     |                                       |              |              |

| Ref.  | CPU          | GPU          | Accel.   | Regression            | Learning     | events       | activity   | Others                                | Softw.       | Hardw.       |

| [9]   | <b>✓</b>     | _            | _        | Linear regr.          | _            | ✓            | _          | _                                     | <b>✓</b>     | _            |

| [48]  | ✓            | _            | _        | Linear regr.          | _            | ✓            | _          | _                                     | ✓            | _            |

| [43]  | ✓            | _            | _        | Linear regr.          | _            | ✓            | _          | _                                     | ✓            | _            |

| [94]  | ✓            | -            | _        | Linear regr.          | _            | ✓            | _          | _                                     | $\checkmark$ |              |

| [90]  | ✓            | -            | _        | Linear regr.          | _            | ✓            | _          | _                                     | ✓            | _            |

| [111] | ✓            | _            | -        | Linear regr.          | _            | <b>√</b>     | _          | Voltage,<br>freq.,<br>CPI             | <b>✓</b>     | -            |

| [77]  | 1            | _            | _        | Linear regr.          |              | ✓            | _          | Voltage,<br>freq.,<br>temp.,<br>state | None         |              |

| [76]  | $\checkmark$ | _            | _        | Linear regr.          | _            | ✓            | _          | Freq.                                 | None         |              |

| [75]  | ✓            | _            | _        | Linear regr.          | _            | $\checkmark$ | _          | Freq.                                 | None         |              |

| [74]  | $\checkmark$ | _            | _        | Linear regr.          | _            | $\checkmark$ | _          | _                                     | None         |              |

| [86]  | ✓            | _            | _        | Linear regr.          | _            | _            | ✓          | _                                     | _            | <b>✓</b>     |

| [71]  | ✓            | _            | _        | Linear regr.,<br>MARS | Neural netw. | _            | ✓          | _                                     | _            | $\checkmark$ |

| [126] | <b>✓</b>     | _            | _        | Linear regr.          | _            | _            | <b>√</b>   | _                                     | _            | <b>√</b>     |

| [125] | ✓            | _            | _        | Linear regr.          | _            | _            | ✓          | _                                     | _            | $\checkmark$ |

| [120] | ✓            | _            | _        | Linear regr.          | _            | _            | ✓          | _                                     | _            | $\checkmark$ |

| [119] | ✓            | _            | _        | Linear regr.          | _            | _            | ✓          | _                                     | _            | $\checkmark$ |

| [70]  | _            | <b>√</b>     | _        | Linear regr.          | _            | ✓            | _          | _                                     | ✓            | _            |

| [20]  | -            | ✓            | _        | _                     | Random for.  | ✓            | _          | _                                     | Virtual      |              |

| [102] | -            | $\checkmark$ | -        | _                     | Neural netw. |              | _          | _                                     | ✓            | _            |

| [66]  | -            | ✓            | -        | _                     | Neural netw. | $\checkmark$ | -          | -                                     | ✓            |              |

| [78]  | _            | ✓            | -        | Linear regr.          | _            | <b>✓</b>     | _          | Voltage,<br>freq.,<br>temp.           | <b>✓</b>     | _            |

| [47]  | -            | _            | ✓        | Linear regr.          | _            | _            | ✓          | _                                     | _            | $\checkmark$ |

| [60]  | _            | _            | <b>√</b> | _                     | Decis. tree  | _            | <b>√</b>   | _                                     | _            | $\checkmark$ |

| [83]  | <b>√</b>     | _            | ✓        | Linear regr.          | _            | _            | ✓          | _                                     | <b>✓</b>     | $\checkmark$ |

| [52]  | ✓            | _            | ✓        | Linear regr.          | _            | _            | ✓          | _                                     | _            | $\checkmark$ |

| [23]  | ✓            |              | ✓        | Linear regr.          | _            | _            | ✓          | _                                     | _            | ✓            |

| [127] | ✓            | -            | ✓        | Linear regr.          | _            | -            | ✓          | _                                     | _            | <b>✓</b>     |

Monitoring implementation. Power statistics related to the switching activity can be monitored either at the software or hardware level, as shown in Figure 2. A software power monitoring (Softw. in Table 1) implementation provides a flexible solution that can be applied in an after-market perspective, since making use of the performance monitoring counters (PMCs) already available in an existing design requires no hardware changes while the computation of the power estimate is carried out at the software level. Software-implemented run-time power monitors, depicted in Figure 2a, leverage the architectural statistics exposed through the PMCs, where a carefully selected subset of such PMCs is periodically read out to compute the power estimates. In contrast, a hardware power monitoring (Hardw.) solution requires to instantiate ad-hoc additional digital hardware elements that operate in a totally isolated manner from the main computing pipeline. As shown in Figure 2b, hardware-implemented run-time power monitors leverage the microarchitectural statistics directly exposed by the hardware platform. In particular, a hardwareimplemented power monitor is an additional hardware component that periodically reads out the switching activity from a selected subset of physical wires to compute the power estimates. The output of the hardware-implemented power monitor can be exposed at the software level through a dedicated performance counter.

## 3.2 Classification of the state of the art

Table 1 classifies the surveyed state of the art according to the four taxonomy dimensions discussed in Section 3.1. A large fraction of the proposed solutions target general-purpose CPUs, while few are aimed at GPUs and hardware accelerators (see **Target** in Table 1). The simplicity of linear regressors makes them the de-facto standard power modeling design choice regardless of the monitored target component, although some proposals also explored learning-based solutions such as neural-network models (see **Family** in Table 1). From the model statistics viewpoint, performance events represent the most exploited source of information to compute the run-time power estimates for both CPUs and GPUs, while circuit-level switching activity is the most used information to feed run-time power monitors targeting hardware accelerators. Notably, there are no proposals in the literature that combine both performance events and toggling activity as the statistics of a run-time power model (see **Statistics** in Table 1). Finally, the majority of run-time power monitors targeting CPUs and GPUs are software-implemented due to the impossibility of modifying the hardware of commercial computing units, while, on the contrary, run-time power monitors targeting hardware accelerators are mainly implemented at the hardware level (see **Implem**. in Table 1).

An extensive discussion of the quality, performance, overheads, and implementation details of each state-of-the-art contribution related to the run-time power modeling and monitoring aspects is provided in Section 4 and Section 5, respectively.

#### 4 POWER MODELING

The run-time power model is at the core of the run-time power monitoring infrastructure since it defines the mathematical function implemented in the power monitor. In particular, the run-time power model represents the identified mathematical function that delivers a periodic estimate of the power consumption of the target computing platform starting from the values of a carefully selected set of statistics that are periodically sampled. Such statistics might be any measurable activity in the target platform satisfying two properties. First, each statistic displays a high correlation with the power consumption of the underlying hardware architecture. Second, the set of selected statistics collectively explains the power consumption.

This section is organized into two parts, with the goal of presenting a taxonomy of the state of the art concerning the run-time power models for edge computing platforms, organized according to three macro-dimensions and evaluated according to three quality metrics. Section 4.1 introduces

the considered quality metrics, defined as the properties that allow comparing the quality of different power models. Section 4.2 discusses the proposals available in the literature, starting from the quality metrics and the dimensions of the taxonomy defined in Section 4.1 and Section 3.1, respectively.

## 4.1 Quality metrics

For each state-of-the-art contribution, this survey considers three quality metrics, i.e., model complexity, accuracy, and training and assessment strategies. Such metrics guide the analysis and evaluation of the literature and allow a direct comparison between the different considered state-of-the-art solutions.

The designers of a run-time power monitor must carefully select the properties of the underlying power model in order to satisfy the requirements and constraints of the overall system and obtain the desired qualities related to power monitoring.

- 4.1.1 Model complexity. The complexity of a selected power model determines the complexity of the corresponding monitoring infrastructure and, therefore, the resulting implementation overheads. In this survey, we employ the number of variables employed as inputs of a power model as a proxy for its complexity (**Complexity** in Table 2).

- 4.1.2 Model accuracy. Accuracy is the degree of closeness of direct or indirect measurements of a quantity to its actual value. It describes systematic errors and measures statistical bias. In this survey, we measure the accuracy of a power model (**Accuracy** in Table 2) as its average estimation error, i.e., the mean relative error for the estimation of the dynamic power consumption.

- 4.1.3 Training and assessment strategies. Identifying (Benchmarks Training in Table 2) and assessing (Benchmarks Assessment) the run-time power model require executing benchmarks on the computing platform under analysis. These benchmarks may be either general-purpose ones or micro-benchmarks. General-purpose benchmarks (Gen.) are meant to mimic realistic applications, thus exhibiting complex software architectures and long execution time. They are commonly used to compare the performance, power consumption, and efficiency of different computing platforms. Micro-benchmarks (Micr.) are small kernels meant to timely and efficiently stress specific components of the computing platform. They are commonly used to test and debug specific portions of a computing platform.

On the contrary, using random stimuli to generate the switching activity patterns and the corresponding power traces is not instead a viable solution for the training and assessment of a power model for two main reasons. On the one hand, generating unconstrained random stimuli can provoke the execution of illegal machine instructions that will never occur during normal operating conditions. On the other hand, covering the entire space of the inputs and internal states using a random stimuli generation requires a large amount of time.

# 4.2 Detailed overview of the state of the art

Table 2 summarizes all the considered run-time power modeling proposals from the state of the art, classifying them according to the target platform, model family, and input statistics dimensions. For each proposal, complexity and accuracy numbers as well as training and assessment strategies are also reported. The state-of-the-art works are ordered primarily according to their target platforms, i.e., CPUs, GPUs, and hardware accelerators, and secondarily according to the employed power statistics, i.e., performance events and toggling activity. In the rest of this subsection, we discuss in more detail such state-of-the-art solutions, in the same order as in Table 2, analyzing their quality metrics and discussing their strengths and weaknesses.

Table 2. Detailed taxonomy of the run-time power modeling state-of-the-art. Legend: √yes, − no, N/A unavailable data; **Complexity** model complexity (see Section 4.1.1); **Accuracy** model accuracy (see Section 4.1.2), average estimation error; **Benchmarks** − **Training/Assessment** training and assessment strategies (see Section 4.1.3), general-purpose benchmarks (**Gen.**), micro-benchmarks (**Micr.**).

|       |                                  | Benchmarks                                  |            |          |          |          |            |  |

|-------|----------------------------------|---------------------------------------------|------------|----------|----------|----------|------------|--|

|       |                                  |                                             | Training A |          | Asse     | ssment   | 1          |  |

| Ref.  | Complexity                       | Accuracy                                    | Gen.       | Micr.    | Gen.     | Micr.    | Section    |  |

| [9]   | 4 N/A                            |                                             | _          | <b>√</b> | _        | <b>✓</b> |            |  |

| [48]  | 9                                | ≤ 8% Compaq<br>≤ 15% Intel                  | ✓          | _        | ✓        | _        |            |  |

| [43]  | 15                               | avg. 3W, ≤ 5.8%                             | _          | <b>√</b> | <b>√</b> | _        |            |  |

| [94]  | 3-5                              | 3.0-4.0% Nehalem<br>3.9-6.1% Atom           | ✓          | _        | ✓        | _        |            |  |

| [90]  | 6                                | 2.8% Cortex-A15<br>3.9% A7 → A15            | <b>✓</b>   | _        | <b>✓</b> | _        |            |  |

| [111] | 6 + 3 (V, F, C)                  | 3.8% Cortex-A7<br>2.8% Cortex-A15           | <b>√</b>   | _        | ✓        | _        | Sec. 4.2.1 |  |

| [77]  | 10 + 4 (V, F, T, C)              | 5% Cortex-A7<br>8% Cortex-A15               | ✓          | _        | ✓        | _        |            |  |

| [76]  | ≤ 4 Cortex-A7<br>≤ 6 Cortex-A15  | ≤ 3% single-thread<br>≤ 7.5% multi-thread   | ✓          | _        | ✓        | _        |            |  |

| [75]  | 1-12                             | 1.46% (1 perf. ev.)<br>1.72% (12 perf. ev.) | ✓          | _        | ✓        | _        |            |  |

| [74]  | 6                                | ≤ 5%                                        | <b>√</b>   | <b>√</b> | <b>√</b> | ✓        |            |  |

| [86]  | 2-8                              | 2%                                          | ✓          | _        | ✓        | _        |            |  |

| [71]  | 1-8 (Linear regr.)<br>1-6 (MARS) | 3.6% (Linear regr.)<br>2.9% (MARS)          | ✓<br>✓     | _        | ✓<br>✓   | _        |            |  |

|       | 1-6 (Neural netw.)               | 4.0% (Neural netw.)                         | ✓          | -        | ✓        | -        | Sec. 4.2.2 |  |

| [126] | 6                                | ≤ 9%                                        | <b>√</b>   | _        | <b>√</b> | _        |            |  |

| [125] | N/A                              | ≤ 1.8%                                      | _          | <b>√</b> | ✓        | _        |            |  |

| [120] | 100-400                          | 6%                                          | _          | <b>√</b> | -        | <b>√</b> |            |  |

| [119] | 100-300                          | 3%                                          | N/A        | N/A      | N/A      | N/A      |            |  |

| [70]  | 13                               | 4.7%                                        | <b>√</b>   | _        | <b>√</b> | _        |            |  |

| [20]  | 22                               | 7.8%                                        | <b>√</b>   | _        | <b>√</b> | _        |            |  |

| [102] | 12                               | 2.1%                                        | <b>√</b>   | _        | <b>√</b> | _        | Sec. 4.2.3 |  |

| [66]  | 12 + 14 (CPU + GPU)              | 4.5%                                        | ✓          | _        | ✓  -     | _        |            |  |

| [78]  | 4 + 3 (V, F, T)                  | 5%                                          | ✓          | _        | <b>√</b> | _        |            |  |

| [47]  | 1655-2050                        | ≤ 5%                                        | _          | _        | _        | -  -     | Sec. 4.2.4 |  |

| [60]  | 10-20                            | 4.4%                                        | _          | _        | _        | _        |            |  |

| [83]  | 1-25                             | ≤ 3%                                        | _          | -        | _        | _        |            |  |

| [52]  | 113                              | ≤ 7%                                        | ✓          | <b>√</b> | <b>√</b> | ✓        | Sec. 4.2.5 |  |

| [23]  | 1-29                             | ≤ 5%                                        | _          | -        | _        | _        | Jec. 4.4.3 |  |

| [127] | N/A                              | ≤ 2.7%                                      | _          | _        | _        | _        |            |  |

- 4.2.1 CPUs Performance events-based power modeling. The first class of state-of-the-art power modeling solutions targets general-purpose CPUs that expose performance monitoring counters (PMCs). While the initial works and most of the subsequent ones focused on linear run-time power models, the state-of-the-art also explored performance-events-based models with higher complexity.

- [9] introduced the concept of estimating the energy consumption of a CPU by exploiting information gathered by PMCs about the activity of the CPU hardware units, e.g., ALU, FPU, cache, and memory. In particular, performance events such as the number of integer and control-flow operations, floating-point operations, and level 2 cache misses were shown to have a linear correlation with the energy consumption of the target platform. The experimental evaluation was carried out on the x86 Intel Pentium II general-purpose CPU [97] and AMD ELAN microcontroller, and it made use of synthetic workloads to train and assess the power model.

- [48] proposed a method to estimate the power consumption of separate components of a CPU from its performance events. Such components include the instruction and data caches, the register file, the integer and floating-point ALUs, the buses, and the branch predictor. It also discussed which PMCs count events are actually relevant for the power consumption and how to estimate event counts for power-relevant events not well supported by the available PMCs. Indeed, since typical performance counters do not capture all the power relevant events, the proposed methodology approximated utilization factors through heuristics depending on the machine structure and on the available PMCs. The experimental evaluation considered the *Intel Pentium Pro* [10, 85] and *Compaq Alpha 21164* [7] CPUs and the training and assessment of the linear power models were carried out by employing general-purpose benchmarks from *SPEC CPU95* [103]. Experimental results highlighted average estimation errors up to 8% and 15% for the *Alpha* and *Pentium* processors, respectively.

- In [43], the authors estimated the power consumption for each of 22 components of a CPU through linear regression models taking performance events as inputs. The total power consumption of the overall processor could then be computed as the sum of the power consumptions of the 22 components plus the idle power consumption of the CPU. This work targeted the *x86 Intel Pentium 4* CPUs, employing micro-benchmarks during the identification phase and then validating the obtained power model on the execution of benchmarks from the *SPEC CPU2000* suite [39] and of three Linux desktop applications. Concerning the *SPEC CPU2000* benchmarks, the identified power model showed a average estimation error of 3W and a maximum error of 5.8W.

- [94] demonstrated the possibility to effectively estimate the dynamic power consumption of both *Intel* high-performance *Nehalem* [101] and low-power *Atom* [37] CPUs by using only three performance events, i.e., the number of fetched instructions, level 1 cache hits, and dispatch stalls. The performance events were fed to a linear power model, which was experimentally validated against the simulated *Wattch* [14] power model. Both training and assessment made use of general-purpose benchmarks from the *SPEC CPU2000* [39], *MiBench* [35], and *MediaBench* [56] suites. Results showed 4% and 6.1% average estimation errors on the *Nehalem* and *Atom* CPUs, which decreased to 3% and 3.9%, respectively, by employing 5 counters. Moreover, the authors showed that, for small differences in architecture type, the expression obtained for one architecture can be used to estimate power on the other, with a small increase, around 3%, of the estimation error.

- [90] proposed a run-time power model that, targeting *ARM big.LITTLE* heterogeneous multi-core CPUs, predicted the power consumption of an application on a target core given its execution profile on the current core. For the smaller *Cortex-A7* cores of the target *big.LITTLE* multi-core, the authors claimed it was not necessary to devise a power model, due to the power consumption ranging between 1.4W and 1.5W across all training benchmarks, therefore showing a negligible variability. On the contrary, the larger *Cortex-A15* showed a power consumption varying between

4.5W and 5.1W, suggesting instead the need to identify a run-time power model. The authors identified therefore a linear regression model that takes as the inputs the amounts of integer and floating-point instructions, the number of instructions per cycle, and the access rates to the L1 data, L2, and main memory levels of the memory hierarchy. Moreover, by employing an inter-core prediction model for miss events, the statistics fetched during the execution on a *Cortex-A7* core can be exploited to estimate the power that would be instead consumed by executing on a *Cortex-A15* core. The authors made use of the *SD-VBS* [110], *SPEC CPU2000* [39], and *SPEC CPU2006* [40] benchmark suites, splitting them into two sets devoted to training and assessment, respectively. On the larger core, the model identified with an average estimation error of 1.2% on the training set showed a 2.6% average estimation error on the test set. The inter-core power model, predicting *Cortex-A15* power from *Cortex-A7* statistics, provided instead a 3.9% average estimation error on the test benchmarks.

[111] proposed a methodology to model power consumption with the PMCs available on *ARM big.LITTLE* multi-core processors. In particular, the authors targeted a SoC that featured *ARM Cortex-A7* and -*A15* CPU cores. This work highlighted the importance of carefully selecting a small subset of PMCs to be used within the power model, due to the need to reduce their number so that they can be monitored simultaneously as well as to avoid redundancy due to correlated events. A good PMC selection corresponds to events that are highly correlated with power but at the same time are not highly correlated with each other. The experimental evaluation employed benchmarks from the *MiBench* [35], *MediaBench* [56], and *Longbottom* [62] suites and the results produced average power estimation errors of 3.8% and 2.8% for *Cortex-A7* and -*A15* CPUs, respectively.

[77] proposed an approach for developing run-time power models that exploited a combination of physical predictors measuring frequency, voltage, and temperature, performance events, and information about the CPU state. The methodology is validated on an *ARM big.LITTLE* heterogeneous architecture. The authors also claimed that tuning the model for every CPU frequency level is much more accurate than having a unified model for all clock frequencies. The accuracy of the developed models was compared with the state-of-the-art, showing average prediction errors of 8% and 5% on *Cortex-A15* and *Cortex-A7*, respectively.

[76] extended the methodology described in [77] with more comprehensive event space exploration and statistical techniques to develop more accurate power models for *ARM big.LITTLE* SoCs compared to previous works [90, 111]. CPU state information was notably not employed as a power statistic, differently from [77], due to the large overhead introduced by its usage. The implemented models, which can be split into single- and multi-thread ones and into intra- and inter-core ones, were evaluated by targeting the *ODROID-XU3* development board, executing *cBench* benchmarks for single-thread models and benchmarks from the *PARSEC* [12] suite for multi-thread ones. Intracore single-thread and multi-thread models reported average estimation errors below 3% and 7.5%, respectively. Notably, the multi-thread models took as their inputs sets of performance events that were completely different from those employed in the single-thread ones.

[75] described an approach to obtain accurate power models on embedded computing platforms which do not expose PMCs. Targeting a *Gaisler LEON3* CPU [3], the authors demonstrated the usage of a soft-core replica implemented on FPGA and enhanced with PMCs to obtain execution statistics and then correlate them with the power consumption measured on the original computing platform. Training made use of the *BEEBS* [84] open-source benchmark suite, specifically designed to assess the performance and energy consumption of embedded-system targets, while the assessment was carried out on a closed-source computer vision algorithm used in space satellite imaging. Experimental results highlighted a 1.46% accuracy error for a model employing the number of store instructions as the lone performance event and a 1.72% one for a model taking 12 events as

its inputs. Moreover, the ability of both models to follow program phases made them suitable for run-time power profiling at the design stage.

[74] modified the *Thumbulator* instruction set simulator to expose performance events in order to model the power consumption of microcontrollers that do not provide access to PMCs. The methodology targeted the *ARM Cortex-M0* microcontroller, and the training and assessment made use of the BEEBS [84] benchmark suite and of 154 micro-benchmarks, extracted from a edge computing application, implementing the various CNN layers with different hyperparameters and optimisations. In particular, the authors identified six performance events, namely executed instructions excluding multiplications, multiplication instructions, taken branches, RAM reads, RAM writes, and flash reads, as run-time power statistics. The resulting models, tailored to different clock frequencies and with knowledge of the activation of prefetch buffers and CPU wait states, provided an average prediction error below 5%.

4.2.2 CPUs - Toggling activity-based power modeling. [86] was one of the first works to exploit the toggling activity of control signals to model the dynamic power consumption. The authors presented a methodology to add hardware counters attached to the control path of the CPU, enabling run-time power monitoring without employing performance events exposed by PMCs, which might also be unavailable on some processors. Indeed, the toggling activity of a subset of identified control signals from the target CPU was shown to have a linear relation with the power consumption. The sum of the measured toggling activity counters, multiplied by coefficients determined within the model identification phase, was therefore shown to be a good estimate of the CPU power consumption. The model training and assessment employed applications from the MiBench [35] benchmark suite, and the estimates were compared to the measures simulated by Synopsys Primepower [107]. The proposed methodology, applied to an existing processor [87], resulted in average power and energy estimation errors of 2% and 1.5%, respectively.

[71] also proposed a methodology to add run-time monitoring of dynamic power consumption in SoCs starting from their RTL description. After generating the dataset of power consumption, signals, and toggling activity from simulation and selecting the optimal set of signals to monitor, and thus employ their toggling activity as the independent variables in the power model, the authors explored the usage of three power models and compared their accuracy as well as the overheads of the corresponding monitoring infrastructure. In particular, the authors evaluated linear regression, multivariate adaptive regression splines (MARS) [27], and neural network models. In their experimental evaluation, they targeted a *SecretBlaze* processor [8] implemented on a *Xilinx Spartan-6* FPGA [2]. The results highlighted the linear model as the best-performing one, when the input is the toggling activity of three signals, with a 3.6% average estimation error. On the contrary, the MARS model with three toggling activity counters showed a 2.9% average estimation error, however with a higher complexity which resulted in higher overheads when employing the power model at run time. Finally, the neural network model achieved a 4% average error, not improving accuracy over both the other models while also requiring a more complex software computation than the linear model.

[126] similarly proposed a dynamic power model, based on toggling activity, designed to be instrumented into an existing RTL design in order to add run-time power monitoring capabilities. To implement such monitoring infrastructure, the described methodology first collected from a simulation the architectural statistics and the related time-based power traces. This information has been used to develop a power model by employing linear regression. Obtaining such linear power model meant identifying the signals which contribute the most to dynamic power consumption and their corresponding weights. The design of the power model considered four figures of merit, i.e., not only the accuracy of the power consumption estimation but also the performance, power,

and area overheads of the implemented monitoring infrastructure. The proposed methodology, while theoretically applicable to any RTL design, was only evaluated by applying it to the *mor1kx* CPU [81]. Applications from the *WCET* [34] benchmark suite were employed for the training and assessment of the power model, which produced an average estimation error of 9%, with a standard deviation of 2%.

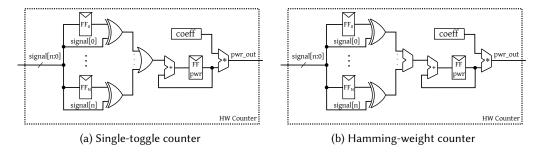

[125] extended the work in [126] to target complex hardware multi-threaded architectures that support single instruction, multiple data (SIMD) parallel processing, such as multi/manycore accelerators and GPUs. The proposed methodology identified power models by solely considering signals that represent either a primary input or output of an RTL module within the design hierarchy. According to the authors, such choice avoided modeling complex non-linear relationship between the power consumption and the internal logic of a hardware module and significantly reduces the computational time required by the model identification. The methodology distinguished between two ways to measure the switching activity of multi-bit signals, with the authors remarking that Hamming-weight counters, which count the number of varying bits for each variation in the signal, are well-suited to measure the switching activity of data signals, while single-toggle counters, that count any change in the target signal, are better tailored to control signals. The methodology was validated on *nu+* [28], a hardware multi-threaded SIMD processor. Notably, and differently from [126], power model identification exploited a set of micro-benchmarks tailored to the target architecture to stress specific parts of the target platform. The assessment phase employed instead the same WCET benchmark suite [34], with the experimental results showing a 1.8% maximum estimation error.

The APOLLO framework proposed in [120] introduced a novel methodology to identify the dynamic power consumption model, which is obtained by applying minimax concave penalty (MCP) regression [124]. The authors targeted an Arm Cortex-A77 core for their experimental evaluation, which highlighted a per-cycle accurate estimation. Both training and assessment are carried out by executing micro-benchmarks. The training set is composed of 300 micro-benchmarks generated automatically through a genetic algorithm (GA)-based framework [36], while the validation set is instead made of 12 micro-benchmarks written by CPU designers to represent different use cases, such as low or high power consumption and CPU throttling. The model obtained in the experimental evaluation employed a number of input variables ranging from 100 and 400, producing an average accuracy error of 6% when executing the micro-benchmarks from the validation set.

[119] proposed the *DEEP* methodology to extend the work in [120]. Rather than operating on multi-bit signals as a single variable, *DEEP* proposes to select model variables at bit level rather than signal level, i.e., signals selected by the linear-regression power model can be any individual bits rather than whole signals. Such solution provides more flexibility in the design space that can be explored, since the number of bits is possibly much larger than the number of signals, which can in general be multi-bit ones. *DEEP* proposes a two-step selection method to identify the variables of the power model. A top-down pruning step based on MCP reduces the number of variables and it is followed by a bottom-up selection algorithm based on best subset selection [67] that produces the set of bits chosen as the model inputs. The authors targeted a 64-bit, single-core CPU for the experimental evaluation of the proposed methodology. Models taking as inputs a number of variables ranging from 100 to 300 produced an accuracy around 3%.

4.2.3 *GPUs - Performance events-based power modeling.* Power modeling approaches followed by state-of-the-art literature also use PMCs in GPUs similarly to those adopted for general-purpose CPUs.

[70] proposed to estimate the power consumption deriving from the execution of a GPU kernel through a linear regression model, where the independent variables are the performance events

collected by the PMCs. Notably, the proposed methodology estimated power consumption at the granularity of kernel calls since the PMCs of the GPU can be accessed only after the completion of each computed kernel. The methodology was demonstrated on *Nvidia CUDA* GPUs [79], training and evaluating the model by using 49 publicly available GPGPU kernels from the *CUDA SDK* and the *Rodinia* benchmark suite [19]. The experimental results highlighted an average estimation error of 4.7%.

[20] applied instead a tree-based random forest method to the run-time power modeling of *Nvidia CUDA* GPUs [79]. The experimental evaluation targeted the *Nvidia GTX280* graphics card, with 52 GPU application kernels from *CUDA SDK*, *Rodinia* [19], and *Parboil* [105] used for training and assessment of the power model. The experimental results showed that the random forest method produced an average estimation error of 7.77%, improving over state-of-the-art regression tree and multiple linear regression methods, both producing 11.7% errors.

The authors of [102] highlighted the shortcomings of employing linear regression models to estimate the power consumption of GPUs, proposing instead the adoption of neural networks (NNs). Among the advantages of modeling GPU power consumption with NNs, they cited their capability to capture non-linear dependencies, their flexibility and adaptability, and their attitude to learn various computation and memory access patterns which makes them suitable to model such a complex architectures. The experimental analysis targeted the *NVIDIA Tesla C2075* and *M2090* GPUs [115] and employed GPU kernels from *CUDA SDK*, *GEM* [32], and the *SHOC* [24] benchmark suite, with the results showing an average power estimation error of 2.1%.

[66] applied deep learning techniques to obtain a power model for a heterogeneous mobile SoC executing parallel applications. The resulting power model was a neural network trained using CPU and GPU PMCs along with actual power measurements by employing a set of OpenGL and OpenCL benchmarks representative of graphics and computing workloads, also used for its evaluation. In particular, the authors targeted a *Intel Z3560* SoC with a *Imagination PowerVR G6430* GPU. The proposed model is a fully connected neural network with four layers, that takes as inputs 14 PMCs from the GPU and 12 from the CPU and provides a power consumption estimate as the output. The model was implemented using the *Keras* framework [22] with *Tensorflow* [1] as its backend. Notably, the GPU utilization PMC is considered as a measure of data coverage of the training dataset. Benchmarks were executed several times with different input sizes under different load conditions until reaching a good coverage of GPU utilization values. The experimental results showed an average estimation error of 4.47% compared to real power measurements, with the authors claiming 3.3× and 2× smaller average estimation errors than state-of-the-art linear regression and NN models.

[78] proposed a power model for the *Nvidia Tegra X1* SoC, that features four *ARM Cortex-A57* high-performance cores coupled with a *Nvidia Maxwell*-based 256-core GPU. The authors distinguished between local events, affecting power consumption in limited regions of the GPU, e.g., the amounts of executed instructions and memory accesses, and global states, affecting global power consumption, e.g., operating frequency, voltage, and temperature. This work aimed to identify a single model that worked for any combination of voltage, frequency, and temperature conditions, making use of only four GPU performance counters. Training was carried out by executing applications from *Rodinia* [19], while the quality of the identified power model was assessed on benchmarks from *CUDA SDK*. Experimental results showed an average accuracy error of 5% for the proposed model, making the quality of its power estimation comparable to the one given by employing different models tailored each to a specific operating clock frequency.

4.2.4 Accelerators - Toggling activity-based power modeling. State-of-the-art run-time power models for hardware accelerators usually exploit the toggling activity of a subset of their signals. Indeed,

hardware accelerators do not usually expose any kind of information about performance events, whether they are designed by hand or generated through high-level synthesis tools.

[47] exploited singular value decomposition (SVD) [31, 53], which is commonly used in machine learning to reduce the number of data dimensions for principal component analysis [112], to identify the correlation between the toggling activity of registers and the power consumption. In particular, SVD highlights which are the most critical registers and how much they contribute to the total power consumption, which is then estimated by a linear model. The power model can then be automatically instrumented to the RTL implementation and synthesized into an FPGA platform, where it is employed for run-time power monitoring. The proposed methodology, which targets generic RTL designs, was validated by considering three FPGA implementations of crypto cores and audio/video encoders/decoders. The obtained power model predicted run-time power consumption with an average estimation error below 5%, compared to a commercial power estimation tool.

[60] proposed a dynamic power consumption model based on decision-tree regression, rather than the traditional linear regression. The methodology targeted hardware accelerators implemented on FPGA, with the goal of instrumenting the identified power model within the RTL design. The proposed methodology is composed of three main steps. First, the most significant signals, i.e., nets in the Verilog HDL netlist exported after place-and-route, are identified through a timing simulation with random-generated input vectors, also filtering the redundant signals. Then, power traces are derived via post-implementation timing simulation. Finally, a decision tree model is identified, tuning its hyper-parameters depending on the desired complexity. The authors claimed that the decision tree is well suited to an area-efficient hardware implementation, since the corresponding series of comparators can be decomposed into a series of if-then-else rules that map effectively to hardware. The experimental results showed an average power estimation error of 4.36%.

4.2.5 CPUs and accelerators - Toggling activity-based power modeling. As the last class of the proposed power modeling taxonomy, we discuss solutions targeting generic RTL designs, i.e., general-purpose CPUs and dedicated hardware accelerators, by applying the same methodology, which exploits toggling activity as the input statistics to the identified run-time power model.

[83] proposed regression models based on toggling activity for both static and dynamic power while instrumenting the RTL level of generic hardware designs, i.e., covering both general-purpose CPUs and hardware accelerators. Concerning dynamic power, the switching activity of an identified subset of registers is exploited to compute the power consumption estimate according to a linear model, whose coefficients are also identified within an automated analysis flow. In addition, the model is retrained after the place-and-route phase that added the corresponding power monitoring infrastructure, allowing to account for variations in power consumption due to its insertion in the RTL design. The methodology was applied to the 32-bit RISC-V [114] *RI5CY* processor [109] and to two hardware accelerators from *OpenCores* that implemented the AES cryptographic algorithm and a FIR filter. The implemented models showed an average estimation error smaller than 3%.

[52] presented a run-time power modeling methodology applicable to any RTL design that automatically identifies the signals that contribute the most to dynamic power consumption through clustering. It leverages the intuition that signals displaying similar toggle patterns will also have a similar contribution to power consumption, hence the modeling error can be reduced by having all the signals from a cluster share the same coefficient in the power model. After clustering signals that showed similar switching activities in the VCD dumps obtained for the execution of benchmark applications from the training set, and thus identifying a smaller number of signals, the methodology produces a linear-regression model with high-order, i.e., > 1 order, terms. The RTL simulation required to collect run-time power traces within the model training phase is further sped up through FPGA acceleration by exploiting the open-source *Strober* framework [51]. Both

micro-benchmarks and general-purpose benchmarks are used for training and assessment purposes. The authors demonstrated their methodology by targeting a heterogeneous processor composed of a Rocket in-order core [6] and a Hwacha vector accelerator [57]. Results are shown for a number of model signals ranging from 40 to 120 and a window size ranging from 80 to 380 clock cycles, and a model with 113 signals and a 340-cycle window size is shown to have the best accuracy.

[23] proposed a linear model based on toggling activity and targeting generic RTL designs, but with a focus on satisfying the resource constraints when implementing the corresponding monitoring infrastructure. The solution considers the impact of the area overhead due to the power monitoring and it allows to implement a model with the desired accuracy, capable to fit a certain budget allocated for its resources, i.e., considering constraints to the amount of FPGA resources that can be devoted to the actual RTL implementation of the power monitor. The methodology was evaluated on HLS-generated [89] hardware accelerators corresponding to kernels from the WCET benchmark suite [34] and on a 32-bit RISC-V single-core CPU [96]. Resource-constrained instances of the power model managed to maintain the average estimation error below 5%.

[127] introduced a methodology to design SCA-resistant power monitors, ensuring that the switching activity of the signals used to compute the power estimates is not a function of the cryptographic keys, plaintexts, and ciphertexts processed within the target computing platform. Such security aspect must be tackled at the model level, i.e., during the identification of the runtime power model. SCA-resistant power monitors targeting a general-purpose computing platform showed an average estimation error in the 1.2%-2.4% range, depending on the temporal resolution, while the ones targeting a HLS-generated hardware accelerator showed a 0.89%-2.7% error range.

#### 5 POWER MONITORING

Run-time power monitors implement the identified power models to deliver online estimates for the power consumption of the target computing platforms. Their implementation can be constrained with respect to *i*) the minimum values for the quality metrics, i.e., temporal resolution and accuracy, and *ii*) the imposed constraints, i.e., area, power, and performance overheads. Regardless of the software or hardware implementation of the power monitor, the activity counters represent the critical components of the entire run-time power monitoring infrastructure. The activity counters are in charge of sampling the activities to feed the power model. In software-implemented power monitors, the performance counter infrastructure defines and implements the activity counters to sample the required architectural statistics, such as the number of executed ALU instructions or cache accesses. In contrast, hardware-implemented power monitors define their own activity counters.

The rest of this section is organized into two parts, with the goal of presenting a taxonomy of the state of the art of run-time power monitors for edge computing platforms that considers two classification dimensions and four quality metrics. Section 5.1 presents first the considered quality metrics, which are the properties that allow comparing the effectiveness of different power monitors. Section 5.2 discusses then the contributions from the literature, starting from the quality metrics and the dimensions of the proposed taxonomy that were defined in Section 5.1 and Section 3.1, respectively.

# 5.1 Quality metrics

This survey analyses the considered state-of-the-art run-time power monitoring solutions according to four quality metrics. They are the temporal resolution and the performance, area, and power overheads. Such metrics guide the analysis of the state of the art and allow evaluating and comparing the solutions proposed by the literature.

Table 3. Detailed taxonomy of the run-time power monitoring state-of-the-art. Legend: — no, N/A unavailable data; **Temp res.** temporal resolution (see Section 5.1.1), sampling period in seconds or clock cycles, (optional) operating frequency of target; **Overheads** — **Perf./Area/Power** performance, area, and power overheads (see Section 5.1.2); [71]: <sup>1</sup> linear, <sup>n</sup> NN, and <sup>m</sup> MARS models, <sup>e</sup> energy overhead; [83]: <sup>r</sup> RI5CY, <sup>a</sup> AES, <sup>f</sup> FIR, <sup>s</sup> SW-based, <sup>h</sup> HW-based power estimation; [127]: <sup>u</sup> unprotected, <sup>p</sup> protected.

|       |                       | Overhe                                                             |                                                |                       |            |  |

|-------|-----------------------|--------------------------------------------------------------------|------------------------------------------------|-----------------------|------------|--|

| Ref.  | Temp. res.            | Perf.                                                              | Area                                           | Power                 | Section    |  |

| [9]   | N/A                   | N/A                                                                | _                                              | _                     |            |  |

| [48]  | 1ms                   | N/A                                                                | _                                              | _                     |            |  |

| [43]  | 440ms                 | N/A                                                                | _                                              | _                     |            |  |

| [94]  | 100K cc               | N/A                                                                | _                                              | _                     | C 501      |  |

| [90]  | 500ms @1GHz           | < 0.5%                                                             | _                                              | _                     | Sec. 5.2.1 |  |

| [111] | 1ms-1s @2GHz          | N/A                                                                | _                                              | ≤ 60mW                |            |  |

| [86]  | 10K cc                | 0.2%                                                               | 4.9%                                           | 3%                    |            |  |

|       |                       | ≥ 0.3% <sup>1</sup>                                                | 1.5-4% <sup>l</sup>                            | 0.8-2% <sup>l,e</sup> |            |  |

| [71]  | 0.1-1ms @25MHz        | $\geq 2\%^n$                                                       | 1.5-3% <sup>n</sup>                            | ≥ 2% <sup>n,e</sup>   |            |  |

|       |                       | $\geq 3\%^{\text{m}}   1.5-3\%^{\text{m}}   \geq 3\%^{\text{m,e}}$ |                                                | ≥ 3% <sup>m,e</sup>   |            |  |

| [126] | 2us @50MHz            | _                                                                  | 6.9%                                           | 4.7%                  | Sec. 5.2.2 |  |

| [125] | 2us @50MHz            | _                                                                  | 9.9% LUT<br>3.9% FF                            | 12mW                  | Sec. 3.2.2 |  |

| [120] | 1cc                   |                                                                    | 0.2%                                           | 0.9%                  |            |  |

| [119] |                       | _                                                                  | 0.04-0.08%                                     | N/A                   |            |  |

|       | Kernel                | N/A                                                                | -                                              | _                     |            |  |

| [20]  | N/A                   | N/A                                                                | N/A                                            | N/A                   |            |  |

|       | 60Hz                  | N/A                                                                | _                                              | < 5W                  | Sec. 5.2.3 |  |

| [66]  | Kernel                | N/A                                                                | _                                              | _                     | 566. 5.2.5 |  |

| [78]  | 500ms                 | N/A                                                                | _                                              | _                     |            |  |

|       | 3001115               | 14/11                                                              | 15.8-25.1%                                     |                       |            |  |

| [47]  | N/A                   | ı                                                                  | 3600-5700 LUT                                  | N/A                   |            |  |

| [60]  | 3us<br>@100MHz        | _                                                                  | ≤ 162 LUT<br>≤ 508 FF<br>≤ 2.5 BRAM<br>≤ 9 DSP | ≤ 6mW                 | Sec. 5.2.4 |  |

|       |                       |                                                                    | 1.4% <sup>r,s</sup>                            | 1.8% <sup>r,s</sup>   |            |  |

|       |                       |                                                                    | 7.1% <sup>r,h</sup>                            | 5.8% <sup>r,h</sup>   |            |  |

| [83]  | 0.1-1ms @800MHz       | $\leq 1.4\%^{\rm s}$ $0\%^{\rm h}$                                 | $0.5\%^{\mathrm{a,s}}$                         | $0.5\%^{a,s}$         |            |  |

| [03]  | 0.1-11118 @8000101112 |                                                                    | 1.8% <sup>a,h</sup>                            | 1.6% <sup>a,h</sup>   |            |  |

|       |                       |                                                                    | 9.7% <sup>f,s</sup>                            | 12.4% <sup>f,s</sup>  | Sec. 5.2.5 |  |

|       |                       |                                                                    | 31.7% <sup>f,h</sup>                           | 22.1% <sup>f,h</sup>  | Sec. 5.2.5 |  |

| [52]  | 80-380 cc             | _                                                                  | N/A                                            | N/A                   |            |  |

| [23]  | 0.02-0.5ms            |                                                                    | Constrained                                    | Prop. to area         |            |  |

| [197] | 0.1-0.5ms             |                                                                    | ≤ 7% <sup>u</sup>                              | ≤ 5.5% <sup>u</sup>   |            |  |

| [14/] | 0.1 0.31113           |                                                                    | ≤ 6% <sup>p</sup>                              | ≤ 5% <sup>p</sup>     |            |  |

The design of a power monitoring infrastructure might optimize different quality metrics depending on the requirements and constraints of the overall system. In general, the optimization

of a quality metric might worsen another one. The designers must indeed carefully consider the trade-offs between the contrasting quality metrics, and, in particular, might aim to minimize the values of each of the four considered quality metrics.

- *5.1.1 Temporal resolution.* Sampling period, corresponding to the difference in time between two consecutive estimates. In this survey, we measure the temporal resolution of a power monitor (**Temp. res.** in Table 3) as either the absolute time in seconds or the number of clock cycles occurring between two samples. For some contributions, the operating frequency of the target platform is also reported in Table 3 for reference.

- 5.1.2 Performance, area, and power overheads. The monitoring infrastructure may present overheads in terms of loss of performance (**Overheads Perf.** in Table 3), due to the use of computing resources, and increased area (**Overheads Area**) and power consumption (**Overheads Power**), originated by the additional hardware logic instantiated to implement the power monitor.

#### 5.2 Detailed overview of the state of the art