# Closed-form Operational Boundaries for Buck Converters With Constant On-Time Control

F. Bizzarri, Senior Member, IEEE, P. Nora, A. Brambilla Member, IEEE,

*Abstract*—In this paper, we provide three operational boundaries in closed analytical form for a Constant ON-Time buck converter working in continuous current mode. Two of these boundaries are related to the sudden appearance of pulse-bursting induced by either (i) the hysteresis of the comparator that drives the input of the block implementing the circuit control algorithm (*hysteresis condition*), or (ii) by a period doubling bifurcation (*bouncing condition*). The third operational boundary corresponds to the *saturation condition* of the circuit controller which does no longer guarantee an OFF-time larger than the minimum allowed one. These stability boundaries are provided both for the *adaptive* and the *fixed* ON-time working modes.

#### I. INTRODUCTION

Switching DC-DC converters are typical hybrid non linear dynamical systems, which play a significant role in nowadays industrial power supply systems. Among possible control strategies of these circuits one can find the ripple-based Constant ON-Time (COT) one. This control scheme has the advantages of simplicity, low cost, fast load transient response, and high conversion efficiency under light-load conditions. COT converters are thus an attractive choice for powering demanding, high-speed digital loads such as FPGAs, ASICs, and CPUs. For the same reasons, COT converters are also largely used in low cost consumer electronics. For a successful design of a COT converter it is mandatory to guarantee that the circuit operates in a *pulse-bursting* free regime [1]–[6], viz. avoiding sub-harmonic oscillations. This is necessary to prevent the undesirable consequences of excessive ripple amplitudes in the inductor current and output voltage waveforms. Furthermore, whenever sub-harmonic oscillations occur, rich frequency spectra are observed that may translate in unpredictable electro-magnetic emissions. These are a well known design aspects, and researches are still working to propose novel analysis techniques and possible technical solutions [7]-[10]. In particular, the availability of operational boundaries, allowing to identify safe regions of operation in the circuit parameter space, is extremely important. Such boundaries are even much more significant if derived and presented in closedform formula, since they represent effective and simple design rules that can be exploited as a first aid in the converter design, for both specific and general purpose applications.

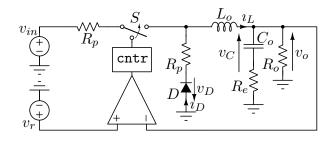

Fig. 1. The schematic of the COT converter.  $R_e$  models the equivalent series resistance (ESR) of the  $C_o$  output capacitor. The  $R_p$  resistors model both the ON-state resistance of the S high-side switch and the D low-side switch.

In [11], the authors derived a straightforward novel sufficient condition, overcoming in term of reliability the popular one presented in [1], [4], and other papers to avoid pulsebursting. In that work the COT buck converter was studied in *fixed* ON-time working mode only. In this paper we consider both the *adaptive* and the *fixed* ON-time working modes. In particular, in the first case the COT control mimics pseudoconstant-frequency regime during steady-state operation by means of a suitable implementation of the ON-phase timer. The basic idea is to calculate the duration of this phase to emulate the duty cycle of a fixed-frequency buck controller.

We provide three operational boundaries in closed analytical form for a COT buck converter working in continuous current mode (CCM) (viz. continuous conduction mode). The converter control algorithm, which involves a minimum OFFphase duration, interplays with the hysteresis of the comparator driving the input of the block implementing the circuit control algorithm. The expression of the *adaptive* ON-time takes into account also possible mismatches of the actual circuit w.r.t. the ideal one.

## II. THE COT BUCK CONVERTER CONTROL ALGORITHM

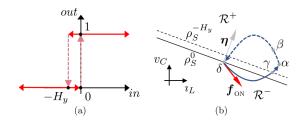

The dynamics of the COT converter state variables  $(i_L, v_C)$  is divided in three phases according to a proper control algorithm. The input variable of the algorithm is the output voltage of the comparator (see Fig. 1) whose generic (in, out) transfer characteristic is reported in Fig. 2(a).

The ON-*phase* starts as soon as, being zero the comparator output, the  $v_r - v_o$  signal gets positive. The controller catches the positive edge of this signal, the output of the comparator becomes positive, and the S switch is closed for the  $\Delta t_{\rm ON}$  fixed ON-time interval. At the end of the ON-phase, S is opened and kept open for the  $\Delta t_{\rm OFF}^{\rm min}$  fixed time interval (minimum OFFphase). This phase is mandatory in many practical designs. At the end of this phase, the controller checks the output of the comparator. If the output is zero, the S switch remains

Federico Bizzarri is with Politecnico di Milano, DEIB, p.za Leonardo da Vinci, n. 32, I20133 Milano, Italy and also with the Advanced Research Center on Electronic Systems for Information and Communication Technologies E. De Castro (ARCES), University of Bologna, 41026 Bologna, Italy (e-mail: federico.bizzarri@polimi.it).

Angelo Brambilla is with Politecnico di Milano, DEIB, p.za Leonardo da Vinci, n. 32, I20133 Milano, Italy. (e-mail: angelo.brambilla@polimi.it) Paolo Nora is with Microchip Technology srl, via Pablo Picasso, n. 41, I20025 Legnano, Italy. (e-mail: paolo.nora@microchip.com)

Fig. 2. (a) Asymmetric hysteretic (*in*, *out*) transfer characteristic of the comparator ( $H_y > 0$ ). (b) A typical CCM steady-state periodic trajectory of the COT buck converter in the ( $i_L, v_C$ ) state plane.  $\eta$  is the unit vector normal to the  $\rho_S^0(i_L, v_C)$  switching manifold and  $f_{ON}$  is the vector field governing the circuit dynamics at the beginning of the ON-phase. Since  $\eta \cdot f_{ON} < 0$ , the trajectory penetrates the  $\mathcal{R}^-$  region.

open (OFF-*phase*) until the condition triggering the ON-phase becomes true again.

Since the comparator is typically characterized by hysteresis, as shown in Fig. 2(a), the OFF-phase can start only if, in the time interval  $\Delta t_{\rm ON} + \Delta t_{\rm OFF}^{\rm min}$ , the  $v_r - v_o$  voltage decreased below the  $-H_y$  threshold, thus resetting the comparator output. If this is not the case, at the end of the minimum OFF-phase a subsequent ON-phase is immediately re-started. In case  $H_y = 0$ , to allow the beginning of the OFF-phase,  $v_r - v_o$ must be still negative at the end of the minimum OFF-phase.

There are many reasons for adding hysteresis to the regulation comparator. For example, one may want to ensure a more "valid" triggering signal for the  $\Delta t_{\rm ON}$  timer, and more generally to improve the switching noise immunity of the regulation circuit. However, as it will be appreciated in the following, a too large hysteresis can introduce undesirable side effects, and other methods for noise immunity enhancement should rather be considered.

In the  $(i_L, v_C)$  state plane (sketched in Fig. 2(b)) the  $v_r - v_o = 0$  and  $v_r - v_o = -H_y$  switching conditions induced by the cntr block leads to the switching manifolds

$$\rho_S^{\epsilon}(i_L, v_C) : v_r - \frac{R_o(i_L R_e + v_C)}{R_e + R_o} = \epsilon \tag{1}$$

where  $\epsilon \in \{0, -H_y\}$ .

In adaptive COT control (i.e., pseudo constant-frequency in CCM operation and low losses), the ON-phase lasts

$$\Delta t_{\rm ON} = \frac{v_o + \frac{s}{k}}{f_{sw}} \frac{p}{q + \frac{v_{in}}{k}} , \qquad (2)$$

where  $v_o$  is the converter output voltage,  $v_{in}$  is the supply voltage,  $f_{sw}$  is the nominal switching frequency, and  $k \in [1, k_{\text{MAX}}]$ . k allows adjusting the desired switching frequency below  $f_{sw}$ , and it is under user control (typically implemented by adding or changing external resistors). The p, q, and s parameters are used to model possible mismatches of the *actual* circuit w.r.t. the ideal one (p = 1, q = s = 0).

Beside non-ideality factors, the ON-time governed by (2) is lower-bounded by a fixed constant value  $\Delta t_{\rm ON}^{\rm min}$ . This means that, whenever  $\Delta t_{\rm ON} < \Delta t_{\rm ON}^{\rm min}$ , the COT buck converter starts working with a non-adaptive ON-time. A minimum controllable ON-time limitation is common in DC-DC converters architectures. The  $v_{in}^{\dagger}$  value of the  $v_{in}$  supply voltage such that the operation mode switches from adaptive to fixed ONtime can be easily inferred from (2).

## III. FUNDAMENTALS OF CCM STEADY-STATE DYNAMICS

The  $i_L$  current is always positive thanks to the D diode in Fig. 1. Actually, in modern architectures such as synchronous buck converters, to enhance converter efficiency the diode is replaced by a low-side MOSFET which is operated as a synchronous rectifier. Consequently, "diode" D, that actually works as a controlled switch in perfect "diode emulation", is modeled as a piecewise-linear ideal component with  $i_D = 0$  for  $v_D \leq 0$  and  $v_D = 0$  for  $i_D \geq 0$ . In the following we assume that the COT buck converter operates in CCM only, consequently  $i_L$  is always positive,  $i_D > 0$ , and thus  $v_D = 0$ .

Figure 2(b) shows a sketch of the typical CCM steadystate evolution of the COT buck converter. This circuit is designed in such a way that the  $v_C$  voltage can be considered almost constant along the periodic steady state behaviour of the circuit, in practice its ripple can be neglected. In particular, being  $\delta \equiv (\bar{\imath}_L, \bar{v}_C)$  in Fig. 2(b) the first point of the ON-phase,  $\bar{v}_C$  can be derived through the  $\rho_S^0(\imath_L, v_C)$  switching manifold exploiting an estimate of  $\bar{\imath}_L$ . An approximation of the latter can be obtained as

$$\bar{\imath}_L = \frac{v_r}{R_o} - \frac{\Delta \imath_L^{\text{oN}}}{2} , \qquad (3)$$

where

$$\Delta i_L^{\text{ON}} = \frac{p\left(\frac{s}{k} + v_r\right) \left(v_{in} - \left(\frac{R_p}{R_o} + 1\right) v_r\right)}{f_{sw} L_o\left(\frac{v_{in}}{k} + q\right)} \tag{4}$$

is the  $i_L$  steady-state ripple approximating as linear w.r.t. time the charging of the inductor, assuming  $v_o$  fixed at  $v_r$  during the entire periodic steady-state evolution of the COT converter, and neglecting the voltage drop across  $R_e$ . In case  $\Delta t_{\rm ON} = \Delta t_{\rm ON}^{\rm ind}$ ,

$$\Delta i_L^{\rm ON} = \frac{v_{in} - \frac{v_r (R_o + R_p)}{R_o}}{L_o} \Delta t_{\rm ON}^{\rm min} .$$

(5)

At the end of the ON-phase, corresponding to  $\alpha$  in Fig. 2(b),  $i_L = \overline{i}_L + \frac{\Delta i_L^{ON}}{2}$ , and the minimum OFF-phase starts (the  $v_{in}$  voltage source is disconnected). At  $\beta$  this phase is concluded and, since the switching boundary  $\rho_S^{-H_y}(i_L, v_C)$  is typically crossed at  $\gamma$ , a point in between  $\delta$  and  $\alpha$ , the comparator output is zero and the OFF-phase is continues.

The transition between CCM and discontinuous current mode (DCM) (viz. discontinuous conduction mode) can be derived by imposing  $\Delta i_L^{ON} = \frac{2v_r}{R_o}$ , which translates in

$$v_{in} - \frac{v_r(2L_o + \Delta t_{\rm ON}(R_o + R_p))}{R_o \Delta t_{\rm ON}} > 0 .$$

(6)

In CCM, the  $T = \Delta t_{\rm ON} + \Delta t_{\rm OFF}$  period of the steady state solution can be achieved by solving the equation  $\Delta i_L^{\rm ON} + \Delta i_L^{\rm OFF} = 0$ , thus deriving

$$\Delta t_{\rm OFF} = \frac{p(s + kv_r)(R_o v_{in} - (R_o + R_p)v_r)}{f_{sw}v_r(R_o + R_p)(kq + v_{in})} , \qquad (7)$$

or, in case  $\Delta t_{\rm ON} = \Delta t_{\rm ON}^{\rm min}$ ,

1

$$\Delta t_{\rm OFF} = \left(\frac{R_o v_{in}}{(R_o + R_p)v_r} - 1\right) \Delta t_{\rm ON}^{\rm min} . \tag{8}$$

## IV. OPERATIONAL BOUNDARIES

#### A. Bouncing condition

The sufficient condition presented in [11] to avoid the pulse-bursting phenomenon was obtained by imposing that the  $\rho_S^0(i_L, v_C)$  switching manifold is reflective for  $i_L \ge 0$ , viz. the periodic steady-state of the circuit belongs to the  $\mathcal{R}^+$  region only (see Fig. 2(b)). It translates in imposing that  $\eta \cdot f_{\text{ON}} > 0$  for  $i_L \ge 0$ , and reduces to guarantee that

$$\bar{\imath}_L(R_o(1+\Theta) - C_o R_e^2(Ro+Rp)) + -(L_o + C_o R_e R_o)\bar{v}_C + CoRe(R_e + R_o)v_{in} > 0 ,$$

(9)

where  $\Theta = L_o - C_o R_e R_p$ . Under the reasonable assumption  $\Theta > 0$ , if (9) is verified for  $\bar{\imath}_L = 0$  then it is satisfied for any  $\imath_L \ge 0$ .

Here we propose to weaken (9) satisfying it in the neighbourhood of  $\bar{\imath}_L$  given in (3). The above constraint can be solved for instance as a function of  $v_{in}$ . Since in general we must have  $v_{in} > v_r$  for step-down operation, assuming  $\Delta t_{\rm ON} > \Delta t_{\rm ON}^{\rm min}$ , and  $R_p \ll R_o$ , it yields

$$v_{in} > \frac{sp\Theta + k(pv_r\Theta - 2f_{sw}C_oR_eL_oq)}{2C_of_{sw}L_oR_e} \equiv v_{in}^{\rm BN} .$$

(10)

In the following we will show numerically that this constraint provides a good estimate of the bifurcation curve marking the loss of stability of the periodic steady-state solution through a period-doubling bifurcation.

In case  $\Delta t_{\rm ON} = \Delta t_{\rm ON}^{\rm min}$ , the constraint in (9), in terms of  $v_{in}$ , simply becomes

$$v_{in} > \frac{R_o + R_p}{R_o} v_r \ . \tag{11}$$

As it will be shown numerically, this condition turns out to be completely non predictive of the appearance of the instability. This means that the sufficient condition derived in [11], cannot be reliably relaxed through the approximation of  $\bar{\imath}_L$ , in case of a non-adaptive ON-time control strategy, at least if one is interested in identifying limit values of the  $v_{in}$  voltage.

#### B. Saturation condition

At steady-state the condition on saturation of the controller implies that the OFF-phase is not allowed since, exactly at the end of the minimum OFF-phase, the  $v_r - v_o$  signal gets positive, viz.  $T = \Delta t_{\rm ON} + \Delta t_{\rm OFF}^{\rm min}$ . The controller saturation is often occurring in transient response. It is an indicator that the COT architecture is fully exploited during load transient, i.e. the rate-of-rise of inductor current cannot be further increased. This operative boundary can be derived by imposing  $\Delta t_{\rm OFF} = \Delta t_{\rm OFF}^{\rm min}$  exploiting (7). As a function of  $v_{in}$  it provides either

$$v_{in} > \frac{v_r (R_o + R_p)((s + kv_r)p + f_{sw}kq\Delta t_{\text{OFF}}^{\min})}{pR_o(s + kv_r) - f_{sw}\Delta t_{\text{OFF}}^{\min}v_r(R_p + R_o)} \equiv v_{in}^*$$

(12)

or, in case  $\Delta t_{\rm ON} = \Delta t_{\rm ON}^{\rm min}$ ,

$$v_{in} > \frac{(R_o + R_p)(\Delta t_{\text{OFF}}^{\min} + \Delta t_{\text{ON}}^{\min})}{R_o \Delta t_{\text{ON}}^{\min}} v_r \equiv v_{in}^* .$$

(13)

## C. Hysteresis condition

The effect of the comparator hysteresis manifests if in the  $\Delta t_{\rm ON} + \Delta t_{\rm OFF}^{\rm min}$  time interval its input does not trespass (decreasing) the  $-H_y$  threshold. Assuming  $v_C = \bar{v}_C$  during the whole COT buck converter working period, the differential comparator input decreases only during the ON-phase, since during this phase the  $i_L$  current increases. This implies that the  $-H_y$  threshold can be properly crossed merely in the  $\Delta t_{\rm ON}$ time interval. To derive an approximate condition to avoid forcing a sudden ON-phase immediately after the minimal OFF-phase, it is sufficient to ensure that the variation of the differential input of the comparator is larger than the  $H_y$ hysteresis window, i.e.,

$$\frac{R_e R_o}{R_e + R_o} \Delta i_L^{\rm ON} > H_y \ . \tag{14}$$

By exploiting Equations (2) and (4), the above inequality can be rewritten as either

$$v_{in} > \underbrace{\frac{pR_e v_r (R_o + R_p)(s + kv_r) + qk f_{sw} H_y L_o (R_e + R_o)}{pR_e R_o (s + kv_r) - f_{sw} H_y L_o (R_e + R_o)}}_{v_{in}^{Hy}}$$

(15)

or, in case  $\Delta t_{\rm ON} = \Delta t_{\rm ON}^{\rm min}$ ,

$$v_{in} > \frac{H_y L_o(R_e + R_o) + R_e(R_o + R_p)\Delta t_{\rm ON}^{\rm min} v_r}{R_e R_o \Delta t_{\rm ON}^{\rm min}} \equiv v_{in}^{Hy} .$$

(16)

From (15) it is clear that, with an adaptive  $\Delta t_{\rm ON}$ , a limit value exists for the  $R_e$  resistance that does not allow the COT buck converter to work for any finite value of  $v_{in}$ , i.e.,

$$R_e^{\rm lim} = \frac{f_{sw} H_y L_o R_o}{p R_o (s + k v_o) - f_{sw} H_y L_o} , \qquad (17)$$

which applies only in case  $pR_o(s + kv_o) - f_{sw}H_yL_o > 0$ .

### V. NUMERICAL RESULTS

In the following subsections two case studies are presented in which some parameter values of the COT buck converter reported in Fig. 1 are fixed,  $v_r = 1.8 \text{ V}$ ,  $C_o = 44 \,\mu\text{F}$ ,  $R_p =$  $73 \,\text{m}\Omega$ ,  $R_o = 1.1 \,\Omega$ , and  $\Delta t_{\text{OFF}}^{\min} = 25 \,\text{ns}$ . Concerning  $\Delta t_{\text{ON}}$  (see (2)),  $f_{sw} = 4 \,\text{MHz}$ , k = 1,  $s = 6.6 \,\text{mV}$ , p = 1, and q = 0,  $\Delta t_{\text{ON}}^{\min} = 125 \,\text{ns}$ . The remaining parameters are left free and used to trace the operational boundaries introduced in Sec. IV. Of course, one may focus on other subsets of free parameters depending on the adopted overall design strategy. Simulation results were obtained by PAN circuit simulator [12], [13] and MPLAB® Mindi<sup>TM</sup> Analog Simulator.

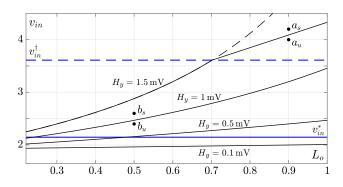

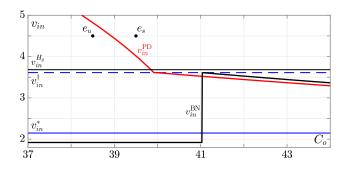

At first, the operational boundaries presented in this paper are graphically represented in the  $(L_o, v_{in})$  parameter plane (see Fig. 3). We have stability above the traces at different values of  $H_y$ . For low values of  $H_y$ , the hysteresis condition turns out to be irrelevant as a function of  $L_o$ , since the saturation condition  $(v_{in}^*)$  is predominant. Nonetheless, for  $H_y \ge 0.5 \,\mathrm{mV}$ , it is evident that the  $H_y$  and  $L_o$  pair must be properly chosen to prevent instability.

By considering the  $H_y = 1.5 \text{ mV}$  case, as soon as the hysteresis boundary crosses the  $v_{in}^{\dagger}$  limit, corresponding to the transition from adaptive to fixed ON-time, a significant change

Fig. 3.  $v_{in}^{\mathsf{T}}$  is the boundary between adaptive (below the dashed line) and fixed ON-time.  $v_{in}^{*}$  represents the *saturation condition*. The black solid curves, for several values of the  $H_y$  hysteresis-window amplitude, represent the *hysteresis condition*.  $R_e = 5 \,\mathrm{m}\Omega$ . *x*-axis:  $L_o \,[\mu\mathrm{H}]$ . *y*-axis:  $v_{in} \,[\mathrm{V}]$ .

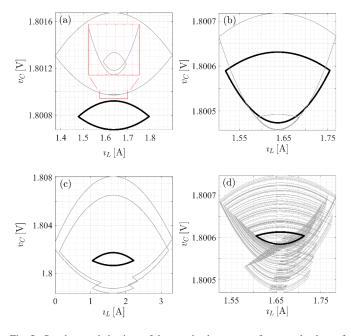

is observed. In particular, adopting a fixed ON-time turns out to be convenient since a wider range of  $v_{in}$  is allowed (the solid curve lie below the dashed one which is the extension of the boundary derived if the adaptive ON-time would still operate). Fig. 3 shows the  $a_s$  and  $a_u$  points corresponding to two different pairs of  $(L_o, v_{in})$  parameters. The former is in the stable region and the latter in the unstable region. The black trajectory in Fig. 5(a) corresponds to the  $a_s$  point in Fig. 3, whereas the grey trajectory corresponds to  $a_u$ . The inset highlights the presence of a "small turn" revealing that the grey orbit exhibits a sub-harmonic oscillation. Analogous considerations can be done for Fig. 5(b) and the  $b_s$ , and  $b_u$ points in Fig. 3. It is interesting to note that even a small amount of hysteresis added to the regulation comparator has a significant impact on the inductance values needed to maintain stable operation across the input voltage range. That is, an apparently harmless change in the internal control circuit might have a dramatic impact on the permissible selection space for external components.

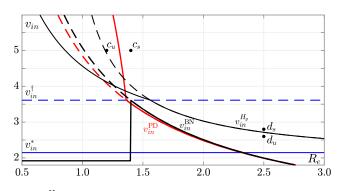

In Fig. 4 the discussed operational boundaries are shown in the  $(R_e, v_{in})$  parameter plane. The  $v_{in}^{H_y}$  thin black line (hysteresis boundary) is the limiting factor until the COT buck converter stops working with an adaptive ON-time, viz.  $v_{in}^{H_y}$ trespasses  $v_{in}^{\dagger}$  from below since both  $v_{in}^*$  and  $v_{in}^{\rm BN}$  (black

Fig. 4.  $v_{in}^{H_y}$  and  $v_{in}^{BN}$  represents the hysteresis condition and the bouncing condition, respectively.  $v_{in}^{PD}$  is a period-doubling bifurcation curve. Dashed segments are the extensions of the solid ones computed with an adaptive ON-time.  $H_y = 1 \text{ mV}$ , and  $L_o = 0.33 \mu\text{H}$ . x-axis:  $R_e \text{ [m\Omega]}$ . y-axis:  $v_{in} \text{ [V]}$ .

thick line, bouncing boundary) lie below such a curve. This remains true for  $R_e$  values larger than that at the intersection between  $v_{in}^{\dagger}$  and  $v_{in}^{\text{BN}}$ . In fact, even if for lower  $R_e$  values the  $v_{in}^{\text{BN}}$  curve abruptly falls at the constant value provided by (11), it can be noticed that such a curve move completely away from  $v_{in}^{\text{PD}}$ . The latter corresponds to the period doubling bifurcation of the CCM periodic steady-state solution.  $v_{in}^{\text{PD}}$  is computed by monitoring the eigenvalues of the monodromy matrix of such a limit cycle, having care of properly resorting to the saltation matrix operator since the circuit is a switching dynamical system exhibiting delayed events too [14], [15]. The  $v_{in}^{BN}$  boundary provides a good approximation of  $v_{in}^{PD}$  in the adaptive ON-time mode. The black trajectory in Fig. 5(c) corresponds to the  $c_s$  point in Fig. 4, whereas the grey trajectory corresponds to  $c_u$ . The shape of the grey orbit reveals that in this configuration the steady-state behaviour of the circuit is far from the "ideal" one in Fig. 2(b). Analogous considerations can be done for Fig. 5(d) and the  $d_s$ , and  $d_u$ points in Fig. 4 (the grey orbit exhibits chaotic dynamics).

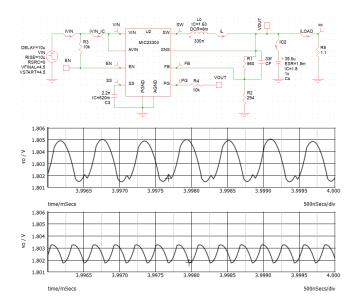

Analogous considerations concerning the bouncing condition and the period doubling bifurcation of the CCM periodic steady-state solution can be done if  $C_o$  is chosen as a variable parameter. The results reported in Fig. 6 were obtained by choosing  $H_y = 1 \text{ mV}$  and  $L_o = 0.33 \mu\text{H}$  as in Fig. 4, and  $R_e = 1.5 \text{ m}\Omega$ . The discussed operational boundaries are shown in the  $(C_o, v_{in})$  parameter plane. It can be noticed that, also in this case, for  $C_o$  values lower than that corresponding to the intersection between  $v_{in}^{\text{BN}}$  and  $v_{in}^{\dagger}$ , the former abruptly falls at the constant value given by (11). We verified the correctness of the stability boundary by performing transient simulations on the on the Mindi<sup>TM</sup> model of the MIC23303 adaptive COT

Fig. 5. Steady state behaviour of the COT buck converter for several values of the circuit parameters. (a):  $L_o=0.9\,\mu\text{H}$ ,  $H_y=1.5\,\text{mV}$ ,  $v_{in}=4\,\text{V}$  (grey curve) and  $v_{in}=4.2\,\text{V}$  (black curve). (b):  $L_o=0.5\,\mu\text{H}$ ,  $H_y=1\,\text{mV}$ ,  $v_{in}=2.4\,\text{V}$  (grey curve) and  $v_{in}=2.6\,\text{V}$  (black curve). (c):  $v_{in}=5\,\text{V}$ ,  $R_e=1.2\,\text{m}\Omega$  (grey curve) and  $R_e=1.4\,\text{m}\Omega$  (black curve). (d):  $R_e=2.5\,\text{m}\Omega$ ,  $v_{in}=2.6\,\text{V}$  (grey curve) and  $v_{in}=2.8\,\text{V}$  (black curve).

Fig. 6. At  $e_u$  and  $e_s$ ,  $v_{in} = 4.5$  V whereas  $C_o = 38.5 \,\mu\text{F}$  and  $C_o = 39.5 \,\mu\text{F}$ , respectively.  $H_y = 1 \,\text{mV}$ ,  $L_o = 0.33 \,\mu\text{H}$ , and  $R_e = 1.5 \,\text{m}\Omega$ . x-axis:  $C_o \,[\mu\text{F}]$ . y-axis:  $v_{in} \,[\text{V}]$ .

buck regulator by Microchip Technology [16]. The schematic of the circuit is reported in the upper panel of Fig. 7. The central panel and the lower panel refer to the  $e_s$  and  $e_u$  points in Fig. 6, and show  $v_o(t)$  (see Fig. 1). At  $e_s$  the steady-state behaviour is periodic and it corresponds to the black limit cycle in Fig. 5. At  $e_u$  chaotic dynamics can be observed as it happens in Fig. 5(d).

## VI. CONCLUSION

Simple algebraic expressions involving circuit parameters of a COT buck converter implementation are derived to check stability. They can be used during a preliminary dimensioning phase to adequately choose COT elements, such as inductor and output capacitor, to determine the extension of the input voltage in wide range applications and how external operating frequency adjustment impacts on stability. The effect of a possible hysteresis of the comparator (internal to the chip) is also considered, and its effects on both stability and the external inductor selection are shown. As such, addition of hysteresis to the regulation comparator should be carefully evaluated during the design of the COT controller.

Fig. 7. Upper panel: Mindi<sup>TM</sup> simulation schematic of the MIC23303 adaptive COT buck regulator by Microchip Technology. Central panel:  $v_o(t)$  at the  $e_u$  point in Fig. 6. Lower panel:  $v_o(t)$  at the  $e_s$

## REFERENCES

- J. Wang, J. Xu, and B. Bao, "Analysis of pulse bursting phenomenon in constant-on-time-controlled buck converter," *IEEE Transactions on Industrial Electronics*, vol. 58, no. 12, pp. 5406–5410, Dec 2011.

- [2] J. Wang, B. Bao, J. Xu, G. Zhou, and W. Hu, "Dynamical effects of equivalent series resistance of output capacitor in constant on-time controlled buck converter," *IEEE Transactions on Industrial Electronics*, vol. 60, no. 5, pp. 1759–1768, May 2013.

- [3] T. Qian, "Subharmonic analysis for buck converters with constant ontime control and ramp compensation," *IEEE Transactions on Industrial Electronics*, vol. 60, no. 5, pp. 1780–1786, May 2013.

- [4] R. Redl and J. Sun, "Ripple-based control of switching regulators—an overview," *IEEE Transactions on Power Electronics*, vol. 24, no. 12, p. 2669–2680, Dec 2009.

- [5] T. Qian, "Subharmonic analysis for buck converters with constant ontime control and ramp compensation," *IEEE Transactions on Industrial Electronics*, vol. 60, no. 5, pp. 1780–1786, 2013.

- [6] —, "Study of subharmonic oscillation mechanism and effect of circuit propagation delay for buck converters with constant on-time control," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 60, no. 3, pp. 788–795, 2013.

- [7] B. Wang, D. Chen, C. J. Chen, and S. F. Hsiao, "Stability prediction of integrated-circuit based constant on-time controlled buck converters," *IEEE Transactions on Power Electronics*, pp. 1–1, 2020.

- [8] W. Liu, C. Chen, C. Cheng, and H. Chen, "A novel accurate adaptive constant on-time buck converter for a wide-range operation," *IEEE Transactions on Power Electronics*, vol. 35, no. 4, pp. 3729–3739, 2020.

- [9] X. Zhang, B. Bao, H. Bao, Z. Wu, and Y. Hu, "Bi-stability phenomenon in constant on-time controlled buck converter with small output capacitor esr," *IEEE Access*, vol. 6, pp. 46 227–46 232, 2018.

- [10] F. Bizzarri, P. Nora, and A. Brambilla, "Load transient response analysis of constant on-time dc-dc converters using a state-variables approach," *IEEE Transactions on Power Electronics*, vol. 35, no. 5, pp. 4489–4499, 2020.

- [11] F. Bizzarri, P. Nora, and A. Brambilla, "A novel sufficient condition to avoid subharmonic oscillations for buck converters with constant on-time control," *Electronics Letters*, vol. 56, no. 6, pp. 305–308, 2020.

- [12] F. Bizzarri, A. Brambilla, G. Storti Gajani, and S. Banerjee, "Simulation of real world circuits: Extending conventional analysis methods to circuits described by heterogeneous languages," *IEEE Circuits and Systems Magazine*, vol. 14, no. 4, pp. 51–70, 2014.

- [13] F. Bizzarri and A. Brambilla, "PAN and MPanSuite: Simulation vehicles towards the analysis and design of heterogeneous mixed electrical systems," in *IEEE International Conference of New Generation of Circuits and Systems (NGCAS)*, Sept 2017, pp. 1–4.

- [14] M. Farkas, *Periodic motions*. New York, NY, USA: Springer-Verlag New York, Inc., 1994.

- [15] F. Bizzarri, A. Brambilla, and G. Storti Gajani, "Extension of the variational equation to analog/digital circuits: numerical and experimental validation," *International Journal of Circuit Theory and Applications*, vol. 41, no. 7, pp. 743–752, 2013.

- [16] MHz PWM 3A Buck Regulator with HyperLight Load<sup>TM</sup> and Power Good, Microchip Technology Inc., 9 2013, rev. 2.0. [Online]. Available: https://www.microchip.com/wwwproducts/en/MIC23303