# Resistive Switching Device Technology Based on Silicon Oxide for Improved ON–OFF Ratio—Part II: Select Devices

Alessandro Bricalli, *Student Member, IEEE*, Elia Ambrosi, Mario Laudato, *Student Member, IEEE*, Marcos Maestro, Rosana Rodriguez, *Senior Member, IEEE*, and Daniele Ielmini<sup>®</sup>, *Senior Member, IEEE*

Abstract—The cross-point architecture for memory arrays is widely considered as one of the most attractive solutions for storage and memory circuits thanks to simplicity, scalability, small cell size, and consequently high density and low cost. Cost-scalable vertical 3-D cross-point architectures, in particular, offer the opportunity to challenge Flash memory with comparable density and cost. To develop scalable cross-point arrays, however, select devices with sufficient ON-OFF ratio, current capability, and endurance must be available. This paper presents a select device technology based on volatile resistive switching with Cu and Ag top electrode and silicon oxide  $(SiO_x)$  switching materials. The select device displays ultrahigh resistance window and good current capability exceeding 2 MAcm<sup>-2</sup>. Retention study shows a stochastic voltage-dependent ON-OFF transition time in the 10  $\mu$ s–1 ms range, which needs to be further optimized for fast memory operation in storage class memory arrays.

Index Terms—Conductive bridge RAM (CBRAM), cross-point array, select device, silicon oxide, storage class memory, volatile switching.

#### I. INTRODUCTION

**C** ROSS-POINT arrays represent a promising architecture to compete with Flash memories in terms of density and bit cost. In a cross-point array, every memory element is located at the intersection between a row and a column electrode wire, therefore achieving a minimum device size of  $4F^2$ , where F is the minimum lithographic feature. Cross-point arrays were proposed for resistive switching (RS) memory (RRAM) [1]–[3] and phase change memory (PCM) [4], [5], both benefitting from a relatively large resistance window and

Manuscript received August 18, 2017; revised October 25, 2017; accepted November 15, 2017. Date of publication December 6, 2017; date of current version December 27, 2017. This work was supported by the European Research Council under Grant ERC-2014-CoG-648635-RESCUE. The review of this paper was arranged by Editor U. E. Avci. (*Corresponding author: Daniele lelmini.*)

A. Bricalli, E. Ambrosi, M. Laudato, and D. lelmini are with the Dipartimento di Elettronica, Informazione e Bioingegneria, Italian Universities Nanoelectronics Team, Politecnico di Milan, 20133 Milan, Italy (e-mail: alessandro.bricalli@polimi.it; elia.ambrosi@polimi.it; mario.laudato@polimi.it; daniele.ielmini@polimi.it).

M. Maestro and R. Rodriguez are with the Universitat Autònoma de Barcelona, 08193 Bellaterra, Spain (e-mail: marcos.maestro@uab.cat; rosana.rodriguez@uab.cat).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2017.2776085

a scalable device size. Similar to Flash memory, 3-D versions of the cross-point architectures have been proposed adopting either horizontal stacking [3], [5], [6] or vertical concepts [7]–[9]. For these reasons, cross-point arrays have scalable bit cost that is required to develop storage class memories with density comparable to Flash [10].

Due to the dense crisscross structure of a cross-point circuit, read and programming operations inevitably lead to disturb effects, such as voltage disturb or sneak paths [1], [3], [11]. In the latter, application of a read/program voltage across a selected memory cell also results in unintended current contributions from half-selected cells, which share either the same row or the same column as the selected device. To mitigate those sneakpaths, each memory element must be accompanied by a select device with high nonlinear characteristic. Due to voltage division across the memory and select elements, most of the applied voltage drops across the high-resistance select device, thus inhibiting the sneak-path leakage.

To minimize sneak-path effects and maximize the available array size, the select device should display a very high ON-OFF ratio, usually estimated as the ratio of the current at the operational voltage (V) and at the half voltage (V/2). The select element should also show sufficiently large current I(V)to enable set/reset operations of the memory element [3], [12], while its endurance and bandwidth should be compatible with the memory element. Also, select devices should be fabricated in the back end of line (BEOL) to enable 3-D stackable or vertical crossbar arrays [13]. To satisfy these multiple requirements, several types of select elements have been proposed, including oxide-based p-n diodes [1], [3], mixed ionic-electronic conduction devices [14], oxide-based tunnel diodes [15], insulator-metal transition layers [2], [16], chalcogenide-based threshold switching devices [5], [17], and threshold vacuum switches [18].

Most recently, novel select devices based on volatile conductive bridge RAM (CBRAM) were demonstrated with both Cu and Ag top electrode (TE) materials. CBRAM with a Cu/SiO<sub>x</sub> structure displays both unipolar and bipolar switching [19], evidencing the capability of ultralow current operation ( $I_C = 10$  pA) [20]. Most recently, volatile switching was shown in Cu/SiO<sub>2</sub> devices below  $I_C = 500 \ \mu$ A, thus supporting Cu/SiO<sub>2</sub> stacks for use in select devices [21], [22]. Volatile switching was also demonstrated in CBRAM with

This work is licensed under a Creative Commons Attribution 3.0 License. For more information, see http://creativecommons.org/licenses/by/3.0/

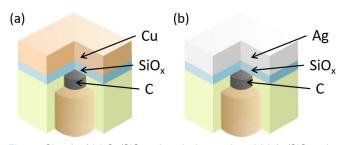

Fig. 1. Sketch of (a)  $Cu/SiO_X$  select device stack and (b) Ag/SiO<sub>X</sub> select device stack.

Ag TE, and attributed to the unstable migration of Ag [21], [23]–[25]. Thanks to the extremely high ON–OFF ratio and low voltage operation, the volatile RRAM with Cu and Ag electrodes might be an excellent select device for  $SiO_x$ -based RRAM with high ON–OFF ratio [26].

This paper presents  $\text{SiO}_x$ -based (with  $x \approx 1$ ) RRAM devices with Cu or Ag TE, exhibiting volatile switching with high ON–OFF ratio up to  $10^7$ . The Ag/SiO<sub>x</sub> device shows bipolar switching after forming and volatile behavior for the compliance current  $I_C$  below 100  $\mu$ A. The retention time has been characterized by time-resolved experiments, indicating large variability of the ON–OFF transition time in a broad range between 10  $\mu$ s and 1 ms. Optimization of the retention time for fast device operation in a cross-point array is discussed.

A preliminary study of the Cu/SiO<sub>x</sub> and Ag/SiO<sub>x</sub> select devices was reported previously in [21]. Here, we provide a fully detailed report, with a deep investigation about the transition from volatile to nonvolatile switching at variable  $I_C$ , about the thickness dependence of volatile switching in Ag/SiO<sub>x</sub>, and about the time evolution of the OFF-state resistance and threshold voltage after switching. This paper further elaborates about the capability of SiO<sub>x</sub>-based RRAM also addressed in the companion paper about nonvolatile memory devices [26].

#### **II. EXPERIMENTAL DEVICES AND SETUP**

Fig. 1(a) shows a schematic of the select devices addressed in this paper, including  $Cu/SiO_x/C$  stack and  $Ag/SiO_x/C$  stack. Each device consists of a one-transistor/one-resistor (1T1R) structure, where the transistor was fabricated in the front end, and was connected to the BEOL select device via a W plug, similar to the RRAM devices in the companion paper [26]. The TE layer (Cu, Ag) and the SiO<sub>x</sub> switching layer were deposited by e-beam evaporation without breaking the vacuum [23]. The bottom electrode (BE) was a graphitic C pillar with a diameter of 70 nm. The metallic TE thickness was 50 nm, while SiO<sub>x</sub> was deposited with various thicknesses  $t_{ox}$ between 3 and 7 nm. A mixed DC/AC experimental setup was used to allow full electrical characterization of the select devices [26]. All devices were characterized after forming, which was carried out at positive voltage, except where noted.

## III. SWITCHING CHARACTERISTICS OF Cu/SiO<sub>x</sub> DEVICES

To analyze the selector properties of our  $Cu/SiO_x$  devices, we first applied a forming step with positive voltage aiming at inducing the formation of conductive filament (CF) by

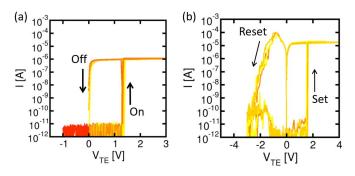

Fig. 2. (a) -V curves for the Cu/SiO<sub>X</sub> stack for  $I_C = 1 \mu A$ . (b) -V curves for the same device for  $I_C = 20 \mu A$ . Increasing  $I_C$  leads to a transition from unidirectional volatile switching to bipolar nonvolatile switching.

injection of Cu cations from the TE. After forming, the device was operated with the same  $I_C$  as in the forming operation, except where noted. Fig. 2(a) shows the measured I-V curves at  $I_C = 1 \ \mu A$ : after reducing the voltage to zero from the ON state, the device displays again OFF state during the subsequent negative and positive voltage sweeps, with constant set voltage  $V_{set} = 1.2$  V. This indicates spontaneous retraction of the CF back to the TE without the need to apply any negative voltage. The spontaneous retraction is possibly due to the buildup of a compressive/tensile stress gradient inducing migration of the Cu CF back to the TE and disconnection of the CF at the BE side [27]. This, however, only occurs at zero bias, as the I-V curves clearly show the presence of an ON state during the whole voltage ramp-down, without any abrupt transition to the OFF state. Such behavior was observed for relatively low  $I_C$ , whereas for  $I_C > 10 \ \mu A$ , the conventional bipolar switching with nonvolatile ON state was recovered [see Fig. 2(b)]. The transition from volatile to nonvolatile switching at relatively high  $I_C$  suggests a threshold value of the CF size, possibly explained by plastic deformation of the  $SiO_x$  matrix and release of the mechanical stress at the CF location, thus reducing the stress-induced instability of the LRS [27]. The ON-OFF ratio approaches 10<sup>8</sup> at the reset voltage  $V_{\text{reset}} = -1.2$  V, namely, from the reset current  $I_{\text{reset}} = 100 \ \mu\text{A}$  to the HRS leakage current in the range of a few picoamperes, the latter being limited by the experimental current sensitivity. However, such a large resistance window is accompanied by extremely low endurance, in the range of a few cycles under DC operation, thus strongly limiting the feasibility of Cu/SiO<sub>x</sub> stack for nonvolatile RRAM.

## IV. SWITCHING CHARACTERISTICS OF Ag/SiO<sub>x</sub> DEVICES

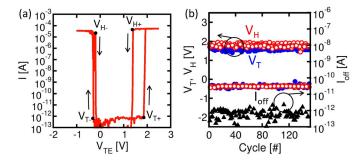

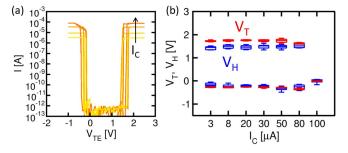

Fig. 3(a) shows the measured I-V curves for CBRAM devices with Ag TE shown in Fig. 1(b). In this case, the device switches to an ON state due to the formation of a Ag CF at a threshold voltage  $V_T \approx 1.9$  V. A relatively high compliance current  $I_C = 50 \ \mu$ A was used in the experiment. As the voltage across the device decreases, the device switches back to the OFF state at a hold voltage  $V_H \approx 1.3$  V, unlike the Cu-SiO<sub>x</sub> device. This suggests that the Ag CF is thinner and/or less stable compared with the Cu case, thus resulting in a more efficient CF retraction at low voltages. Also, for Ag/SiO<sub>x</sub>, a

Fig. 3. (a) Measured I-V curves for the Ag/SiO<sub>x</sub> stack. (b) Measured  $V_T$ ,  $V_H$  (for both positive and negative bias), and  $I_{OFF}$  as a function of the number of cycles.

Fig. 4. (a) Measured I-V characteristics for the Ag/SiO<sub>X</sub> stack, where a negative sweep was applied first, followed by forming under positive voltage which could lead to bidirectional volatile switching. (b) Sketch of the CF structure where positive-voltage forming and successive retraction of the CF results in the formation of a BE reservoir, enabling bidirectional switching from both electrode sides.

bipolar switching behavior was observed with smaller threshold voltage at negative bias of about  $V_T \approx -0.4$  V. Fig. 3(b) shows the measured  $V_T$  and  $V_H$  for 150 DC cycles for both positive and negative bias, showing the markedly asymmetric switching with smaller negative  $V_T$  and  $V_H$ . The figure also shows the subthreshold leakage current  $I_{\text{OFF}}$  at 1 V, indicating a stable leakage below 1 pA, which suggests that the whole CF was dissolved after each switching event. Data indicate an ON-OFF ratio exceeding 10<sup>7</sup>, limited by the instrumental sensitivity of  $I_{\text{OFF}}$ .

#### A. Explanation of Bidirectional Switching

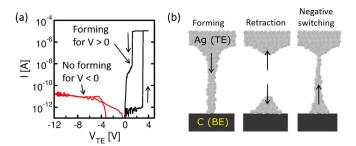

Given the strongly asymmetric structure of the device, similar to the Cu/SiO<sub>x</sub> stack in Section III, we investigated the origin of bipolar switching in Fig. 4. To better understand the origin of bipolar switching, we tested the possibility to form the device under negative voltage. Fig. 4(a) shows the I-V curve measured on a pristine device during a negative voltage sweep to  $V_{\text{TE}} = -12$  V. In this case, no forming event was observed, thus suggesting that the BE has no active role in the switching mechanism in Ag/SiO<sub>x</sub> devices. A positive voltage sweep was then applied evidencing a forming event at  $V_{\text{TE}} = 3$  V. After the forming process, application of a negative voltage revealed low voltage switching, thus demonstrating bipolar switching behavior only following positive forming.

The lack of negative forming and the onset of bidirectional switching after positive forming can be explained by the phenomena sketched in Fig. 4(b). First of all, application of a positive voltage leads to a forming process, consisting in the

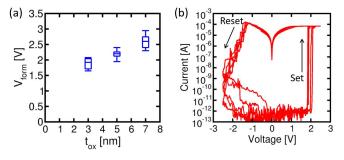

Fig. 5. (a) Forming voltage as a function of the SiO<sub>x</sub> thickness. (b) Example of RS behavior for a sample with  $t_{ox} = 3$  nm.

Fig. 6. (a) Measured *I*-*V* curves for the Ag/SiO<sub>x</sub> stack at increasing  $I_C$ . (b)  $V_T$  and  $V_H$  as a function of  $I_C$ , showing volatile switching for  $I_C = 80 \ \mu$ A and below, whereas switching at  $I_C = 100 \ \mu$ A led to permanent ON state ( $V_T = 0 \ V$ ).

injection of Ag cations into the  $SiO_x$  layer, thus creating a conductive bridge to the BE. As the bias is removed, the CF spontaneously disrupts, thus deactivating electrical connection between TE and BE. However, a significant amount of Ag atoms remain segregated at the BE side, which then can serve as a reservoir for RS upon application of a negative voltage. A similar incorporation of Ag clusters within the oxide layer in RRAM has been recently observed by high-resolution TEM [24], which supports our interpretation of bidirectional switching in Ag/SiO<sub>x</sub> devices.

#### B. Impact of tox

Oxide thickness plays a key role in controlling the switching characteristics of the Ag/SiO<sub>x</sub> device. Fig. 5(a) shows the forming voltage  $V_{\text{form}}$  of Ag/SiO<sub>x</sub> devices as a function of  $t_{\text{ox}}$ , ranging from 3 to 7 nm. The forming voltage increases with thickness, which is consistent with the field-driven breakdown process at the origin of forming [26]. After forming, we observed a tendency to nonvolatile switching in the case of the device with the thinnest oxide  $t_{\text{ox}} = 3$  nm. This is shown in Fig. 5(b), reporting a set of switching characteristics indicating bipolar switching with positive voltage set and negative voltage reset transitions. On the other hand, devices with a thicker oxide showed bidirectional volatile switching behavior similar to data in Section IV-A. In the following, data will refer to the device with  $t_{\text{ox}} = 5$  nm.

## C. Impact of I<sub>C</sub>

Volatile switching based on metallic filament formation has been previously demonstrated [18], [28], although typically at relatively low compliance current  $I_C$  which is not relevant

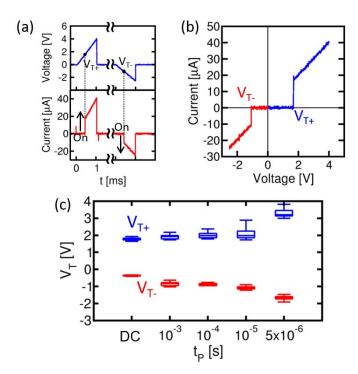

Fig. 7. (a) Measured voltage (top) and current (bottom) oscilloscope traces, (b) corresponding I-V curves, and (c) measured  $V_{T+}$  and  $V_{T-}$  as a function of  $t_P$ . The threshold voltage increases at decreasing  $t_P$  in agreement with the time dependence of migration dynamics in CBRAM and RRAM.

enough for practical use as select element in crossbar arrays. To study the impact of  $I_C$  on volatile switching, Fig. 6(a) shows the switching characteristics of the  $Ag/SiO_x$  device for increasing  $I_C$  between 3 and 100  $\mu$ A. For each value of  $I_C$ , we carried out 20 bipolar cycles (only one representative I-V curve is shown in the figure), and the  $V_T$  and  $V_H$  values were collected. Fig. 6(b) shows the average values of  $V_{T+}$ (positive threshold voltage),  $V_{T-}$  (negative threshold voltage),  $V_{H+}$  (positive holding voltage), and  $V_{H-}$  (negative holding voltage) as a function of  $I_C$ . Volatile switching is observed below or equal to 80  $\mu$ A, whereas application of higher  $I_C$ leads to permanently ON state ( $V_T = V_H = 0$  V). Different from the  $Cu/SiO_x$  stack, the device could not be reset to the OFF state by negative voltage sweep. The volatile switching at  $I_C \approx 80 \ \mu A$  in Fig. 6 supports the use of Ag/SiO<sub>x</sub> device as select element for the Ti/SiO<sub>x</sub> RRAM [26], thus enabling all-SiO<sub>x</sub> 1S1R for crossbar arrays of nonvolatile memories.

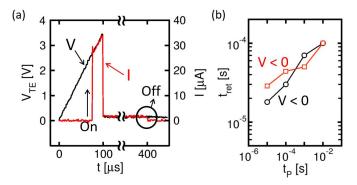

#### V. PULSED CHARACTERISTICS

The pulsed characteristics of  $Ag/SiO_x$  selector were studied both in terms of the switching characteristics and the pulsewidth dependence of the threshold voltage  $V_T$ . Fig. 7(a) shows the voltage and current oscilloscope traces collected with the experimental setup described in [26]. An arbitrary waveform generator was used to apply triangular voltage pulses to the 1T1R structure, while the current was monitored by measuring the voltage drop across the 50- $\Omega$  input resistance of an oscilloscope connected to the BE terminal. Triangular voltage pulses were used to monitor the threshold voltage, with a pulsewidth  $t_P = 1$  ms. The threshold voltage was taken in correspondence of the steep current rise during positive sweep to 4 V and negative sweep to -2.5 V, where the lower negative voltage is due to the asymmetric characteristics of the bipolar switching. Fig. 7(b) shows the corresponding I-Vcurve, which was obtained by combining the collected voltages and currents from the oscilloscope trace at equal times along the leading edge of the triangular pulse. Between one cycle and the other, the device was left unbiased for as long as ten times the duration of the switching pulse, to ensure that the Ag CF was completely dissolved after switching. Note the highly linear characteristic in the ON state suggesting ohmic transport in the CF. The returning I-V curves for decreasing voltage were not detected because of the vertical trailing edge of the voltage pulse in Fig. 7(b). The gate voltage was kept constant during both positive and negative voltage pulses.

Fig. 7(c) shows the extracted  $V_{T+}$  and  $V_{T-}$  as a function of the pulsewidth. Threshold voltages in the pulsed regime are higher than the DC counterpart and increase for decreasing pulsewidth, which is a well-known behavior in CBRAM and RRAM devices [29]. The value of  $V_{T+}$  increases from 2 V in the DC case up to more than 3 V for voltage pulses with  $t_P = 5 \ \mu$ s, while  $V_{T-}$  increases from -0.5 to -2 V.

#### **VI. RETENTION TIME**

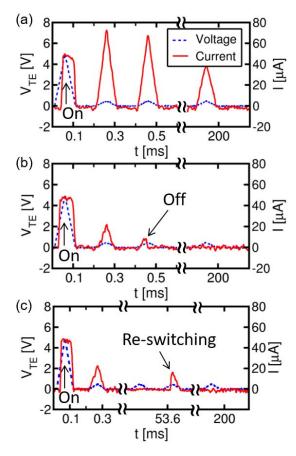

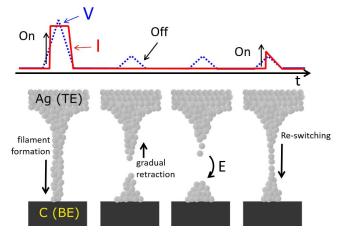

Data in Fig. 7(a) show vertical OFF-ON transition indicating that the switching time was extremely fast. However, also the ON-OFF transition time is highly relevant for select devices, as all previously selected memory cells in the cross-point array must readily become unselected after access. In the Ag/SiO<sub>x</sub> device, the ON–OFF transition time is limited by the retention time of the Ag CF, which takes some time to dissolve after its formation. To study the retention time of the Ag CF, we applied an initial triangular pulse with  $t_P = 1$  ms and amplitude  $V_{\text{TE}} = 5$  V to switch the device in the ON state, then we monitored the resistive state of the device at increasing times by measuring the current in response to 1000 subsequent triangular pulses with  $t_P = 1$  ms and  $V_{\text{TE}} = 0.5$  V. This switch/read experiment was repeated 100 times on the same device to analyze the cycle-to-cycle variation of the retention time. Fig. 8 shows three representative behaviors that were observed on the same device. In Fig. 8(a), the device remains in the ON state for the whole duration of the reading pulses, while gradual dissolution of the CF and final transition to the OFF state were observed in Fig. 8(b). Immediate transition to the OFF state before the first read pulse was also detected (not shown). In the latter case, we occasionally observed a "reswitching" of the device induced by one of the read pulses, as shown in Fig. 8(c). This can be explained by a gradual disappearance of the CF, even in the case of apparent OFF state, as sketched in Fig. 9. As the CF is gradually dissolving by retraction toward the Ag TE, the application of the relatively small read voltage across the small depleted gap induces sufficient electric field to allow reformation of the CF. In this scenario, random local redistribution of Ag clusters at zero bias may play a key role in the reswitching process, as specific spatial configurations may favor Ag ions rediffusion toward the BE when a small

Fig. 8. Voltage and current traces during a retention time experiment, indicating three types of behavior, namely (a) permanent ON state during the measurement, (b) gradual transition from ON to OFF state, and (c) transition to OFF state, followed by reswitching to the ON state after some time.

Fig. 9. Sketch for the reswitching behavior, where the CF is first formed, then gradually dissolves, until the application of a low-voltage positive pulse causes switching to the ON state.

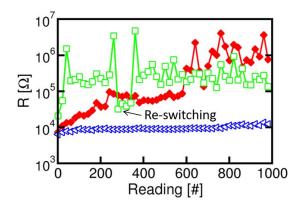

read voltage bias is applied. Fig. 10 summarizes the three representative behaviors by showing the measured resistance during the 1000 read pulses, including permanent ON state, gradual ON–OFF transition, and reswitching.

Given the stochastic nature of the CF dissolution, the process was studied systematically for various  $t_P$  values, as shown in Fig. 11(a). First, a triangular pulse with amplitude

Fig. 10. Measured R as a function of number of reading pulses for the retention experiments as the ones shown in Fig. 8, including permanent ON state, gradual transition from ON to OFF state, and reswitching behavior.

Fig. 11. (a) Oscilloscope traces of voltage and current for measuring the retention time  $t_{ret}$ . (b) Measured  $t_{ret}$  as a function of  $t_P$  for both positive and negative switching.

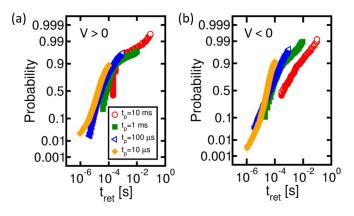

$V_{\rm TE}$  = 3.5 V was applied to induce switching to the ON state, then the voltage was changed abruptly to a constant read value  $V_{\text{read}} = 0.1$  V to monitor the resistive state of the device.  $V_{\text{read}}$  was chosen to prevent any additional disturb to the device and enable spontaneous switching OFF. During the first set operation, a relatively low gate voltage  $V_G = 1.5$  V was used to limit the maximum current to about  $I_C = 50 \ \mu A$ . On the other hand, a larger gate voltage  $V_G = 3$  V was used during read to minimize the series resistance of the transistor, which accounts for the read current being larger than the set current in Fig. 8(a). The read pulse was  $t_{read} = 10t_P$ to include the large statistical variation of retention times. During  $t_{read}$ , the current was continuously monitored with the oscilloscope to allow for the detection of the retention time  $t_{ret}$  in correspondence of the read current dropping to zero [see Fig. 11(a)], revealing the dissolution of the CF. To improve the signal-to-noise ratio, the current was measured via a transimpedance amplifier. Fig. 11(b) shows the average  $t_{ret}$  as a function of  $t_P$ , where  $t_{ret}$  increases for increasing  $t_P$ . This is in agreement with previous observations, where the retention time was improved for increasing the set time [24], [27], which was explained as the release of the compressive stress affecting CF retention due to Joule heating during the set pulse [27]. Retention time under positive and negative switching cycles confirms the same qualitative and quantitative behaviors. Fig. 12 shows the cumulative distributions of  $t_{\rm ret}$

Fig. 12. Cumulative distribution of  $t_{ret}$  for (a) positive voltage switching and (b) negative voltage switching, for increasing  $t_P$ .

for increasing  $t_P = 10 \ \mu$ s, 100  $\mu$ s, 1 ms, and 10 ms. For all values of  $t_P$ , the distributions show a large statistical spread, indicating a broad cycle-to-cycle variation of the switching OFF dynamics for the same device. Reducing the retention time and controlling its statistical variation remain vital objectives to improve the performance of Ag-based select device for implementation in the future cross-point arrays of resistive memories.

### **VII. CONCLUSION**

This paper presents a novel volatile CBRAM device using  $Cu/SiO_x$  and  $Ag/SiO_x$  stacks. While  $Cu/SiO_x$  stack only shows unipolar select operation at relatively low currents,  $Ag/SiO_x$  indicates excellent bidirectional select operation with ON-OFF ratio exceeding  $10^7$  and maximum current around  $80 \ \mu$ A, which is fully compatible with low-current  $Ti/SiO_x$  RRAM. The device was characterized in pulsed regime to evaluate the threshold voltage and retention time, the latter indicating a broad distribution in the range of  $1 \ \mu s-10$  ms. Reducing and controlling the retention time remain a key challenge for Ag-based select devices for future crossbar array applications. More research work at the levels of materials engineering and pulse algorithm will be needed to improve the performance for practical use in memory technology.

#### REFERENCES

- I. G. Baek *et al.*, "Multi-layer cross-point binary oxide resistive memory (OxRRAM) for post-NAND storage application," in *IEDM Tech. Dig.*, Dec. 2005, pp. 750–753, doi: 10.1109/IEDM.2005.1609462.

- [2] M.-J. Lee *et al.*, "Two series oxide resistors applicable to high speed and high density nonvolatile memory," *Adv. Mater.*, vol. 19, pp. 3919–3923, Nov. 2007, doi: 10.1002/adma.200700251.

- [3] M.-J. Lee *et al.*, "2-stack 1D-1R cross-point structure with oxide diodes as switch elements for high density resistance RAM applications," in *IEDM Tech. Dig.*, Dec. 2007, pp. 771–774, doi: 10.1109/IEDM.2007. 4419061.

- [4] Y. Sasago *et al.*, "Cross-point phase change memory with 4F<sup>2</sup> cell size driven by low-contact-resistivity poly-Si diode," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2009, pp. 24–25.

- [5] D. Kau *et al.*, "A stackable cross point phase change memory," in *IEDM Tech. Dig.*, Dec. 2009, pp. 1–4, doi: 10.1109/IEDM.2009.5424263.

- [6] M.-C. Hsieh *et al.*, "Ultra high density 3D via RRAM in pure 28 nm CMOS process," in *IEDM Tech. Dig.*, Dec. 2013, pp. 3–10, doi: 10.1109/IEDM.2013.6724600.

- [7] H. S. Yoon *et al.*, "Vertical cross-point resistance change memory for ultra-high density non-volatile memory applications," in *Proc. IEEE Symp. VLSI Technol.*, Aug. 2009, pp. 26–27.

- [8] I. G. Baek *et al.*, "Realization of vertical resistive memory (VRRAM) using cost effective 3D process," in *IEDM Tech. Dig.*, Dec. 2011, pp. 31.8.1–31.8.4, doi: 10.1109/IEDM.2011.6131654.

- [9] H.-Y. Chen, S. Yu, B. Gao, P. Huang, J. Kang, and H.-S. P. Wong, "HfO<sub>x</sub> based vertical resistive random access memory for cost-effective 3D cross-point architecture without cell selector," in *IEDM Tech. Dig.*, Dec. 2012, pp. 7–20, doi: 10.1109/IEDM.2012.6479083.

- [10] G. W. Burr, B. N. Kurdi, J. C. Scott, C. H. Lam, K. Gopalakrishnan, and R. S. Shenoy, "Overview of candidate device technologies for storage-class memory," *IBM J. Res. Develop.*, vol. 52, nos. 4–5, pp. 449–464, 2008, doi: 10.1147/rd.524.0449.

- [11] E. Linn, R. Rosezin, C. Kügeler, and R. Waser, "Complementary resistive switches for passive nanocrossbar memories," *Nature Mater.*, vol. 9, pp. 403–406, Apr. 2010, doi: 10.1038/nmat2748.

- [12] F. Nardi *et al.*, "Control of filament size and reduction of reset current below 10 μA in NiO resistance switching memories," *Solid-State Electron.*, vol. 58, pp. 42–47, Apr. 2011. [Online]. Available: https://doi.org/10.1016/j.sse.2010.11.031

- [13] G. W. Burr et al., "Access devices for 3D crosspoint memory," J. Vac. Sci. Technol. B, Microelectron. Process. Phenom., vol. 32, p. 040802, Jul. 2014. [Online]. Available: http://dx.doi.org/10.1116/1.4889999

- [14] R. S. Shenoy *et al.*, "MIEC (mixed-ionic-electronic-conduction)-based access devices for non-volatile crossbar memory arrays," *Semicond. Sci. Technol.*, vol. 29, p. 104005, Sep. 2014. [Online]. Available: https://doi.org/10.1088/0268-1242/29/10/104005

- [15] W. Lee *et al.*, "Varistor-type bidirectional switch (J<sub>MAX</sub>> 10<sup>7</sup> A/cm<sup>2</sup>, selectivity~10<sup>4</sup>) for 3D bipolar resistive memory arrays," in *Proc. IEEE Symp. VLSI Technol. (VLSIT)*, Jul. 2012, pp. 37–38, doi: 10.1109/VLSIT.2012.6242449.

- [16] M. Son *et al.*, "Excellent selector characteristics of nanoscale VO<sub>2</sub> for high-density bipolar ReRAM applications," *IEEE Electron Device Lett.*, vol. 32, no. 11, pp. 1579–1581, Nov. 2011, doi: 10.1109/LED. 2011.2163697.

- [17] M.-J. Lee *et al.*, "A plasma-treated chalcogenide switch device for stackable scalable 3D nanoscale memory," *Nature Commun.*, vol. 4, Oct. 2013, Art. no. 2629, doi: 10.1038/ncomms3629.

- [18] C. Ho et al., "Threshold vacuum switch (TVS) on 3D-stackable and 4F<sup>2</sup> cross-point bipolar and unipolar resistive random access memory," in *IEDM Tech. Dig.*, Dec. 2012, pp. 2–8, doi: 10.1109/IEDM.2012. 6478968.

- [19] C. Schindler, S. C. P. Thermadam, R. Waser, and M. N. Kozicki, "Bipolar and unipolar resistive switching in Cu-Doped SiO<sub>2</sub>," *IEEE Trans. Electron Devices*, vol. 54, no. 10, pp. 2762–2768, Oct. 2007, doi: 10.1109/TED.2007.904402.

- [20] C. Schindler, M. Weides, M. N. Kozicki, and R. Waser, "Low current resistive switching in Cu–SiO<sub>2</sub> cells," *Appl. Phys. Lett.*, vol. 92, p. 122910, Mar. 2008. [Online]. Available: http://dx.doi.org/10.1063/1. 2903707

- [21] A. Bricalli, E. Ambrosi, M. Laudato, M. Maestro, R. Rodriguez, and D. Ielmini, "SiO<sub>x</sub>-based resistive switching memory (RRAM) for crossbar storage/select elements with high on/off ratio," in *IEDM Tech. Dig.*, Dec. 2016, pp. 4.3.1–4.3.4, doi: 10.1109/IEDM.2016.7838344.

- [22] W. Chen, H. J. Barnaby, and M. N. Kozicki, "Volatile and nonvolatile switching in Cu-SiO<sub>2</sub> programmable metallization cells," *IEEE Electron Device Lett.*, vol. 37, no. 5, pp. 580–583, May 2016, doi: 10.1109/LED.2016.2540361.

- [23] J. Song, J. Woo, A. Prakash, D. Lee, and H. Hwang, "Threshold selector with high selectivity and steep slope for cross-point memory array," *IEEE Electron Device Lett.*, vol. 36, no. 7, pp. 681–683, Jul. 2015, doi: 10.1109/LED.2015.2430332.

- [24] Z. Wang *et al.*, "Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing," *Nature Mater.*, vol. 16, pp. 101–108, Sep. 2017, doi: 10.1038/nmat4756.

- [25] R. Midya *et al.*, "Anatomy of Ag/Hafnia-based selectors with 10<sup>10</sup> nonlinearity," *Adv. Mater.*, vol. 29, p. 1604457, Mar. 2017, doi: 10.1002/adma.201604457.

- [26] A. Bricalli, E. Ambrosi, M. Laudato, M. Maestro, R. Rodriguez, and D. Ielmini, "Resistive switching device technology based on silicon oxide for improved on-off ratio—Part I: Memory devices," *IEEE Trans. Electron Devices*, vol. 65, no. 1, pp. 115–121, Jan. 2018.

- [27] S. Ambrogio, S. Balatti, S. Choi, and D. Ielmini, "Impact of the mechanical stress on switching characteristics of electrochemical resistive memory," *Adv. Mater.*, vol. 26, pp. 3885–3892, Jun. 2014, doi: 10.1002/adma.201306250.

- [28] W. Banerjee *et al.*, "Occurrence of resistive switching and threshold switching in atomic layer deposited ultrathin (2 nm) aluminium oxide crossbar resistive random access memory," *IEEE Electron Device Lett.*, vol. 36, no. 4, pp. 333–335, Apr. 2015, doi: 10.1109/LED.2015.2407361.

- [29] S. Larentis, F. Nardi, S. Balatti, D. C. Gilmer, and D. Ielmini, "Resistive switching by voltage-driven ion migration in bipolar RRAM—Part II: Modeling," *IEEE Trans. Electron Devices*, vol. 59, no. 9, pp. 2468–2475, Sep. 2012, doi: 10.1109/TED.2012.2202320.

Alessandro Bricalli (S'16) received the B.S. and M.S. degrees in engineering physics from Politecnico di Milan, Milan, Italy, in 2013 and 2015, respectively, where he is currently pursuing the Ph.D. degree in electrical engineering.

His current research interests include fabrication and electrical characterization of RRAM devices for memory application and beyond-CMOS computing systems.

**Elia Ambrosi** received the B.S. and M.S. degrees in electrical engineering from Politecnico di Milan, Milan, Italy, in 2013 and 2016, respectively, where he is currently pursuing the Ph.D. degree in electrical engineering.

His current research interests include electrical characterization and modeling of resistive switching devices for novel memory and computing architectures.

Mario Laudato (S'15) received the M.S. degree in electrical engineering from Politecnico di Milan, Milan, Italy, in 2014, where he is currently pursuing the Ph.D. degree in electrical engineering with a focus on nonvolatile emerging memories and select devices for high density cross-point memory and neuromorphic computing.

Marcos Maestro received the bachelor's degree in physics from the Universidad de Salamanca, Salamanca, Spain, in 2009, the master's degree in physics instrumentation from the Universidad de Valladolid, Valladolid, Spain, in 2012, and the master's degree in micro and nanoelectronic and the Ph.D. degree in electronic engineering and telecommunications from the Universitat Autonoma de Barcelona, Bellaterra, Spain, in 2013 and 2017, respectively.

His current research interests include the study of resistive switching phenomenon observed in different materials and the feasibility of its application in diverse fields such as memories, logic, or neuromorphic.

Rosana Rodriguez (SM'13) received the Ph.D. degree in electrical engineering from Universitat Autònoma de Barcelona, Bellaterra, Spain, in 2000.

She is currently an Associate Professor with the Universitat Autònoma de Barcelona. Her current research interests include the electrical characterization and reliability of CMOS devices, and the study of the resistive switching phenomenon and its applications.

Daniele lelmini (SM'09) received the Ph.D. degree in nuclear engineering from Politecnico di Milan, Milan, Italy, in 2000.

He joined the Dipartimento di Elettronica, Informazione, e Bioingegneria, Politecnico di Milan, as an Assistant Professor in 2002 and an Associate Professor in 2010, where he has been a Professor since 2016. He conducts research on emerging nanoelectronic devices, such as phase change memory and resistive switching memory.

Dr. lelmini received the Intel Outstanding Researcher Award in 2013, the ERC Consolidator Grant in 2014, and the IEEE EDS Rappaport Award in 2015.