# Brain-inspired computing via memory device physics ©

Cite as: APL Mater. 9, 050702 (2021); doi: 10.1063/5.0047641 Submitted: 15 February 2021 • Accepted: 11 April 2021 • Published Online: 10 May 2021

D. lelmini,<sup>1,a)</sup> D. Z. Wang,<sup>2,b)</sup> and Y. Liu<sup>2,c)</sup>

# **AFFILIATIONS**

<sup>1</sup> Dipartimento di Elettronica, Informazione e Bioingegneria, Politecnico di Milano and IU.NET, Piazza L. da Vinci 32, 20133 Milano, Italy

<sup>2</sup>Key Laboratory for UV Light-Emitting Materials and Technology (Northeast Normal University), Ministry of Education, Renmin Street, 5268 Changchun, China

a) Author to whom correspondence should be addressed: daniele.ielmini@polimi.it

<sup>b)</sup>Email: wangzq752@nenu.edu.cn

<sup>c)</sup>Email: ycliu@nenu.edu.cn

# ABSTRACT

In our brain, information is exchanged among neurons in the form of spikes where both the space (which neuron fires) and time (when the neuron fires) contain relevant information. Every neuron is connected to other neurons by synapses, which are continuously created, updated, and stimulated to enable information processing and learning. Realizing the brain-like neuron/synapse network in silicon would enable artificial autonomous agents capable of learning, adaptation, and interaction with the environment. Toward this aim, the conventional microelectronic technology, which is based on complementary metal–oxide–semiconductor transistors and the von Neumann computing architecture, does not provide the desired energy efficiency and scaling potential. A generation of emerging memory devices, including resistive switching random access memory (RRAM) also known as the memristor, can offer a wealth of physics-enabled processing capabilities, including multiplication, integration, potentiation, depression, and time-decaying stimulation, which are suitable to recreate some of the fundamental phenomena of the human brain *in silico*. This work provides an overview about the status and the most recent updates on brain-inspired neuromorphic computing devices. After introducing the RRAM device technologies, we discuss the main computing functionalities of the human brain, including neuron integration and fire, dendritic filtering, and short- and long-term synaptic plasticity. For each of these processing functions, we discuss their proposed implementation in terms of materials, device structure, and brain-like characteristics. The rich device physics, the nano-scale integration, the tolerance to stochastic variations, and the ability to process information *in situ* make the emerging memory devices a promising technology for future brain-like hardware intelligence.

© 2021 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/). https://doi.org/10.1063/5.0047641

# I. INTRODUCTION

The human brain is one of the most complex objects in the universe. It is capable of executing high-level cognitive tasks, such as abstraction, generalization, prediction, decision making, recognition, and navigation in a continuously changing environment. Such high cognitive capability of the brain comes at the expense of an extremely low power consumption of only 20 W. There are mainly two reasons for the high energy efficiency of the brain: First, information exchange and processing are event driven; therefore, spiking energy is consumed only when and where it is needed. Second, neurons and synapses are co-located within the same, highly interconnected neural network, where each neuron is connected to other  $10^4$  neurons, on the average. Neuron/synapse co-location means that data processing, consisting of synaptic excitation and neuron firing, and memory, consisting of the synaptic weight and the neuron threshold, share the same location within the brain.<sup>1</sup>

Many research efforts aim at mimicking the type of computation of the human brain to achieve its outstanding energy efficiency. This is the objective of neuromorphic engineering, where spiking neural networks (SNNs) are developed with artificial neurons and synapses. SNNs generally adopt the same fully connected (FC) architecture of the conventional perceptron networks pioneered by Rosenblatt and Minsky.<sup>2,3</sup> In a SNN, however, neurons and synapses usually display a time-dependent response to the applied spikes, such as integration and fire in a neuron and excitatory post-synaptic current (EPSC) across a synapse. This is different from the conventional artificial neural networks (ANNs) used in artificial intelligence (AI) accelerators for computer vision and speech recognition, where the information is synchronous and based on the amplitude of the signal, instead of its time.<sup>4</sup>

Most SNNs generally rely on the complementary metal-oxide-semiconductor (CMOS) technology, with two main significant advantages: First, the CMOS technology is widely available in the semiconductor industry ecosystem, including design, fabrication, and qualification, therefore creating the conditions to make CMOS-based neuromorphic engineering a mature topic. Second, the CMOS transistor can scale down according to Moore's law, where a reduction of the lithography feature size allows for a larger density and a better performance of the circuit. On the other hand, there are significant limitations in CMOS technology. For instance, time-dependent functions such as spike integration in an artificial neuron generally require large capacitors in CMOS technology, therefore limiting the cost effectiveness of neuromorphic circuits.<sup>5</sup> Synaptic weights are generally stored in static random access memory (SRAM), which are volatile, i.e., all synaptic values are lost when the circuit is switched off.<sup>6</sup> In addition, SRAM devices are large and binary, i.e., they can only store 0 and 1; thus, they are not suitable for gradual potentiation and depression that are typical of synaptic plasticity phenomena.7-

To overcome these limitations, neuromorphic materials and devices are intensively explored to complement CMOS technology. The aim of this new wave of research is to reproduce bioneurological phenomena typical of the human brain with device physics. For instance, phase change materials have been shown to accumulate applied voltage spikes and consequently change their resistivity, which can be used as the physical mechanism for integrate-and-fire (I-and-F) neurons without capacitors.<sup>10-12</sup> The fire process of the typical I-and-F neuron can be reproduced in a nanoelectronics device by abrupt current switching at the onset of the negative differential resistance (NDR) region, such as the electronic threshold switching in ovonic threshold switch (OTS) elements<sup>13</sup> or ferroelectric transition in HfO<sub>2</sub>.<sup>14</sup> Similarly, all other key mechanisms in the biological neural network can be emulated by specifically engineered devices through their physics. The objective is the recreation of a brain-like circuit system with extremely low power consumption and compact, scalable architecture.

This work provides an overview about the status on the development of neuromorphic devices that emulate biological neural processes by device physics. The work will focus on the resistive switching random access memory (RRAM) as the device technology for the implementation of various neuromorphic functions, including artificial synapses, neurons, and dendrites. Circuits demonstrating the full neuromorphic function, such as unsupervised learning and pattern recognition, will also be presented. The rest of this paper is organized as follows: Sec. II will illustrate the major categories of RRAM devices in terms of the switching mechanism and device structure. Section III will provide an overview of the neuromorphic processes and their implementation in RRAM devices. Section IV will deal with artificial neurons with integration, fire, oscillations, and dendritic filtering capability. Finally, Sec. V will focus on artificial synapses including learning functions via plasticity and sensing/computation via short-term memory (STM).

## **II. RESISTIVE SWITCHING DEVICES**

Urged by the scaling limitation of CMOS-based memories, various types of emerging memory devices have been proposed in the last 20 years. These include phase change memory (PCM),<sup>15</sup> magnetic random access memory (MRAM),<sup>16,17</sup> ferroelectric random access memory (FERAM),<sup>18,19</sup> and RRAM.<sup>20–22</sup> These memories have the ability to change their resistance state by a permanent modification of the active material, thus serving as scalable nonvolatile device for standalone and embedded memories.<sup>23–25</sup>

Among the novel emerging memory technologies, RRAM has attracted strong research interest partly due to the simple structure that allows for a relatively straightforward fabrication in academic laboratories and integration within the industrial CMOS process. RRAM has been recognized as a potential technology for synaptic connections in ANNs and SNNs, thanks to the small size, easy integration, and scalability that allow for high connectivity within the neural network.<sup>26</sup> The high synaptic density is further supported by the ability of 3D integration by array stacking<sup>27</sup> of vertical structures.<sup>28–32</sup> The programming energy of RRAM is generally low, thus enabling energy-efficient computation and reconfiguration of the neural network.<sup>31</sup>

## A. Two-terminal devices

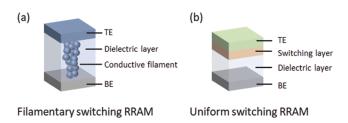

Figure 1 shows a schematic illustration of the two-terminal RRAM device, including a filamentary switching RRAM (a) and a uniform switching RRAM (b). While both devices are based on a metal-insulator-metal (MIM) structure with a top electrode (TE), a bottom electrode (BE), and at least one dielectric layer, the switching mechanisms are fundamentally different. In the

FIG. 1. Illustration of two-terminal resistive switching memory (RRAM) devices for neuromorphic computing. (a) Filamentary RRAM, where the device resistance is changed due to the formation and modulation of a conductive filament across a high resistance dielectric layer. The filament can connect the top electrode (TE) and the bottom electrode (BE) in the low-resistance state (LRS), whereas the filament is disconnected between TE and BE in the high-resistance state (HRS). (b) Uniform switching RRAM, where the device resistance is controlled by a switching layer, usually a metal oxide, which shows a high resistance, due to a low concentration of defects, in the HRS, or a low resistance, due to high concentration of defects, in the LRS.

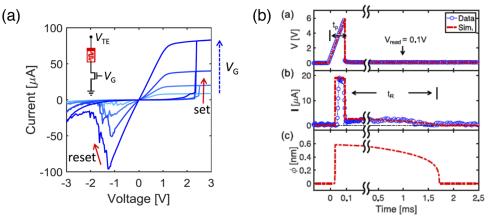

filamentary structure, a forming process is first applied by applying a relatively large voltage that leads to soft breakdown of the MIM.<sup>22</sup> The breakdown spot, consisting of a filamentary path with low resistivity, is then subjected to set/reset processes by the application of voltage pulses. Typically, the RRAM device shows a bipolar switching characteristic, where the applied electric field across the conductive filament causes ionic migration and a consequent change in resistance.<sup>33</sup> For instance, a negative voltage applied to the TE leads to the migration of positively ionized defects toward the TE, thus resulting in depletion of defects at the BE side with an increase in resistance, or reset transition.<sup>34</sup> A positive voltage applied to the TE results in migration of the defects toward the BE, thus refilling the depleted gap and causing a decrease in resistance, or set transition.<sup>34</sup> Filamentary set transition is generally abrupt due to the positive feedback in the gap filling process: As the defects start to migrate toward the gap, the electric field increases, thus causing an acceleration of the ionic migration. To avoid uncontrolled filament growth during the abrupt set transition, usually a transistor is added in series with the RRAM device to enable current limitation below a certain compliance current I<sub>C</sub>.<sup>35</sup> Figure 2(a) shows typical I–V characteristics for a HfO<sub>2</sub> RRAM device with a 1T1R structure.<sup>36</sup> As I<sub>C</sub> increases, the device conductance in the low-resistance state (LRS) increases, thus indicating a larger size of the conductive filament. The reset current correspondingly increases as a result of the larger filament size. The adoption of the one-transistor/one-resistor (1T1R) structure of the RRAM device thus allows for low current operation and tight control of the device conductance, which is beneficial for analog in-memory computing.<sup>3</sup>

Depending on the electrode materials, the conductive filament can be stable for long time even at high temperature<sup>37</sup> or be metastable due to defect diffusion after the set transition.<sup>38–44</sup> In particular, RRAM with Ag TE generally tends to display this type of volatile behavior due to the spontaneous diffusion of Ag from the filament location. This was attributed to surface diffusion of Ag to minimize the total energy of the filament by minimizing the surface to volume ratio.<sup>45</sup> Figure 2(b) shows the typical pulsed programming characteristics for the Ag/SiO<sub>2</sub> RRAM device.<sup>44</sup> Under a triangular pulsed of applied voltage, the device shows a set transition, marked by the abrupt rise of current to the I<sub>C</sub> level. After the pulse, the read current remains active for a finite retention time t<sub>R</sub> of about 1.5 ms, thus revealing the spontaneous decay of the conductive filament diameter  $\phi$  [see simulation results at the bottom of Fig. 2(b)].44 Such a volatile behavior has been proposed for selector elements in a crosspoint device,<sup>46</sup> thanks to the steep switching slope and extremely large on/off ratio exceeding 10 orders of magnitude.<sup>42</sup> However, due to the relatively long retention time in the range between 1  $\mu$ s and several ms, the device is most suitable as a physics-based neuromorphic device to implement transient biological phenomena, such as short-term memory<sup>47</sup> and spike-timing dependent plasticity (STDP).41

The filamentary set/reset process causes intrinsic variability issues due to individual defect diffusion and instability.48-51 Variations include cycle-to-cycle changes of conductance, due to the variability in filament shape and volume,<sup>48</sup> and device-to-device variations due to the difference in the structure and geometry among various RRAM devices.<sup>49</sup> Generally, device-to-device variation plays the key role in technology reliability due to the sensitivity to the local defect concentration, dielectric film microstructure, interface roughness, and filament shape originating from the breakdown event at forming.<sup>50</sup> In addition to programming variations, read variation causes the device resistance to vary even after the device has undergone the set/reset process. The resistance can, in fact, display timedependent fluctuations such as random telegraph noise (RTN) and random walk due to defect instability.<sup>51</sup> The conductance variations can cause a degradation of neural network accuracy,<sup>52,53</sup> although some stochastic computing algorithms may take advantage from noise.54-59

FIG. 2. Filamentary RRAM characteristics. (a) Measured I–V characteristics of a filamentary RRAM device with a 1T1R structure and HfO<sub>2</sub> switching layer. As the compliance current I<sub>C</sub> increases, the filament conductance increases due to the increased size. (b) Pulsed characteristic of a volatile RRAM device, including applied voltage (top), response current (center), and calculated filament diameter (bottom). After the set transition at time 0, the filament spontaneously retracts to the electrodes, thus resulting in a fast drop of conductance within a retention time t<sub>R</sub> of about 1.5 ms. Reprinted with permission from Sun *et al.*, IEEE Trans. Electron Devices **67**, 1466 (2020). Copyright 2019 IEEE.

Note that variations are not intrinsic to filamentary switching, rather they arise generally in most types of memory

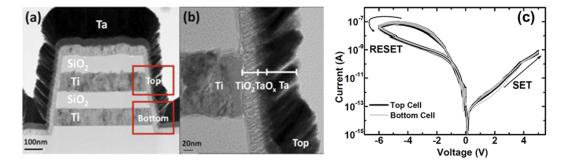

FIG. 3. Uniform switching RRAM structure and characteristics. [(a) and (b)] Device structure, including vertical Ta TE, TaO<sub>x</sub>/TiO<sub>2</sub> stack as switching/dielectric layers and horizontal Ti BE. The TE and oxide bi-layer are deposited on the side wall of a stack of multiple BE/SiO<sub>2</sub> layers for a cost-effective vertical RRAM structure.<sup>30</sup> (c) I–V curves of uniform switching for top and bottom cells.<sup>30</sup> From Hsu *et al.*, *IEEE International Electron Devices Meeting (IEDM)*, pp. 10.4.1–10.4.4. Copyright 2013 IEEE. Reprinted with permission from IEEE.

technologies. For instance, PCM displays programming variations due to the stochastic nature of nucleation and growth in the crystallization process.<sup>60</sup> Similarly, FERAM shows variations in the multilevel conductance due to the stochastic switching of individual ferroelectric domains.<sup>61</sup> However, filamentary RRAM is more critically affected by post-programming fluctuations of the resistance, as a result of the localized conduction at atomically thin channels, where trapping, detrapping, and atomic relaxation can induce a strong variation in the device resistance.<sup>62</sup> To mitigate the cycleto-cycle variations, a new concept of filamentary switching RRAM was developed, where the conductive path originates from threading dislocations within epitaxially grown SiGe layers on Si substrates.62 The material-based approach to induce switching at predetermined channels is extremely promising for reducing the programming variations, although post-programming variations at the dislocation filament may still be a concern for reliability.

The conductance variations and their impact on the neural network accuracy can be mitigated by the uniform switching RRAM in Fig. 1(b). The conductance in this device changes as a result of oxygen vacancy exchange at the interface between two oxide layers, the dielectric layer and the switching layer.<sup>64</sup> For instance, the switching layer can consist of an interfacial oxide layer between an active electrode, e.g., Sm, and a relatively high conductive oxide layer, such as La<sub>0.7</sub>Ca<sub>0.3</sub>MnO<sub>3</sub> (LCMO).<sup>65</sup> Figure 3 shows a possible implementation of a uniform switching device with a vertical structure.<sup>30</sup> The device stack includes a Ta TE, TaO<sub>x</sub>, TiO<sub>2</sub>, and Ti BE. The bipolar switching takes place by the oxygen exchange between the TaO<sub>x</sub> and TiO<sub>2</sub> layers. Figure 3(c) shows the I–V curves of the uniform switching device, indicating a smooth and gradual change of resistance.<sup>30</sup> Thanks to the gradual set/reset dynamics, the uniform switching is suitable to perform pulsed potentiation/depression for analog artificial synapses.<sup>30,66</sup> In addition, the low conductance around 100 nS in uniform switching allows for an extremely low energy per spike below 10 fA.<sup>31</sup>

## **B.** Three-terminal devices

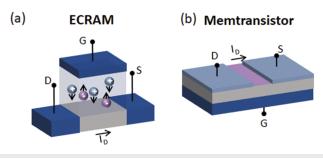

The need for analog conductance, low variation, and low energy in neuromorphic circuits has stimulated the study of advanced three-terminal devices based on ionic migration. Figure 4(a) shows a

APL Mater. 9, 050702 (2021); doi: 10.1063/5.0047641 © Author(s) 2021

three-terminal device called electro-chemical random access memory (ECRAM).<sup>67</sup> The ECRAM displays a transistor structure with gate, source, and drain contacts, where the read path is from the source to drain, while the programming takes place by gate pulses. Application of positive/negative gate pulses results in the migration of ionized defects from a reservoir, close to the gate terminal, to the channel between the source and the drain. Defects can be either Li<sup>+</sup> impurities<sup>68-70</sup> or H<sup>+71,72</sup> or oxygen ions/vacancies.<sup>73,74</sup> Li<sup>+</sup> intercalation and oxygen exchange within the channel can change its conductivity, thus resulting in weight potentiation or depression. ECRAM devices, also referred to as redox transistors or ionic transistors, are characterized by extremely low conductance in the range from few nS<sup>69</sup> to few  $\mu$ S,<sup>73</sup> thanks to the low mobility and low carrier concentration in the channel material, e.g., WO<sub>3</sub>. Such a low conductance is essential to minimize the signal current within the synaptic array, thus enabling low parasitic IR drop<sup>67</sup> and small size of the circuit periphery to handle the output current, including select transistors and integrating capacitances. Most importantly, the potentiation and depression characteristics are extremely gradual and linear, thanks to the bulk conduction mechanism in the device<sup>74</sup> and for accurate integration in I-and-F neurons. On the other hand,

FIG. 4. Illustration of three-terminal devices. (a) ECRAM, where the channel conductance changes by the field-induced migration of ionized defects, such as Li<sup>+</sup>, protons or oxygen vacancies. (b) Mem-transistor, where the conductance is controlled by the migration of defects across a 2D semiconductor channel. Reprinted with permission from D. Ielmini and G. Pedretti, Adv. Intell. Syst. **2**, 2000040 (2020). Copyright 2020 John Wiley & Sons, Inc.

the ECRAM technology usually requires selector devices to properly execute program and read operations.  $^{72}$

Figure 4(b) shows the mem-transistor device, where the channel consists of a 2D semiconductor region with atomic thickness.<sup>75,76</sup> The drain current of the device can be modulated by applying a suitable gate voltage, thanks to the semiconductor properties of transition metal dichalcogenides (TMDs) such as MoS<sub>2</sub>.<sup>77</sup> In addition, the application of a large drain bias can lead to a persistent modification of the channel conductivity due to migration of defects such as grain boundaries<sup>75,76</sup> or Li<sup>+</sup> impurities.<sup>78</sup> The mem-transistor thus allows, in principle, both the transistor effect (by gate stimulation) and memory effect (by drain stimulation), which can support various neuromorphic functions, such as synaptic potentiation/depression and spike dependent plasticity.<sup>75</sup>

#### **III. NEUROMORPHIC PROCESSES BY DEVICE PHYSICS**

Memory devices allow to embody neurobiological processes within a single device with extremely compact size and highly biorealistic properties. This is made possible by the rich physics of the emerging memory devices, where the electric/magnetic polarization, phase structure, and local chemical composition contribute to the electrical conductance, which is, in turn, affected by atomic/ionic drift/diffusion, electro-chemical redox reactions, phase transitions, dielectric breakdown phenomena, and ferroelectric/ferromagnetic transitions.

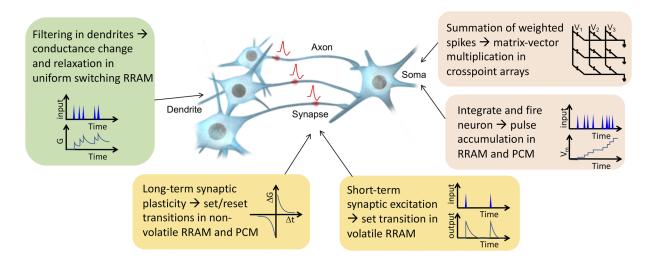

Figure 5 shows a summary of neurobiological features and functions and their respective implementation in resistive memory devices. Generally, neurons in the biological neural network of the human brain consist of soma, dendrites, and an axon. The temporal spikes containing the incoming information are collected by dendrites and processed by the soma. Depending on the incoming stimulation and the type of information processing, e.g., I-and-F

with a characteristic threshold, the neuron can fire, i.e., send an output spike through the axon toward the receiving neurons. The spike transmission from a neuron axon to other neuron dendrites takes place via a synapse, called axo-dendritic synapse, each having a specific weight and a corresponding weight update behavior. The synaptic weight describes the efficacy of an input spike to stimulate the receiving neuron. Synapses display synaptic plasticity, namely, the ability to change their weight in response to the stimulation. Although the synaptic plasticity mechanism is not yet fully understood, several plasticity rules have been proposed, including spike-timing dependent plasticity (STDP)7,9,79-81 and triplet-based plasticity,<sup>8,82,83</sup> where the timing of spikes, e.g., their respective delay or relative frequency, dictates the potentiation or depression of the synapse. Synaptic plasticity controls learning within the human brain; thus, it is of utmost importance in all neuromorphic circuits.

To implement the individual elements of Fig. 5, several devices, circuits, and their respective physics can be adopted. The summation and integration functions of the soma can be implemented in hardware by matrix vector multiplication (MVM) in crosspoint arrays and integration in nanoscale memory devices. Time-dependent dendrite filtering and synaptic plasticity effects can be described by the switching properties of RRAM devices. The rich physics of memory devices and their combination can thus be used to reproduce neuro-biological phenomena at the nanoscale, which benefits the massive connectivity, high scalability, and low-cost of neuromorphic circuits.

## **IV. HARDWARE NEURONS**

The neuron soma can be described by the popular McCulloch–Pitts model,<sup>84</sup> where the neuron input is given by the weighted summation of the incoming spike, while the output

FIG. 5. Illustration of various possible circuit/device implementations of neuro-biological processes. The neuron soma weighted summation can be reproduced by the matrix vector multiplication (MVM) in crosspoint array circuits, while integration of I-and-F neurons is mimicked by pulse accumulation mechanisms in PCMs and RRAMs. The filtering function of dendrites is described by the conductance change and relaxation of uniform switching RRAMs. Short- and long-term plasticity of biological synapses can be implemented by set/reset dynamics of volatile/nonvolatile RRAMs or PCMs.

signal is given by a suitable nonlinear activation function. This can be expressed by the following formula:

$$y_i = f\left(\sum_j w_{ij} x_j\right),\tag{1}$$

where  $y_i$  is the output of the post-synaptic neuron *i*, *f* is the activation function,  $w_{ij}$  are the weights of the synapses connecting presynaptic neurons *j* with the postsynaptic neuron *i*, and  $x_j$  is the signal of the pre-synaptic neuron *j*. While other models, such as the Hodgkin–Huxley (HH) model,<sup>85</sup> are more accurate in the description of the temporal shape of the spike and the bio-chemical details of Ca and K ion transport, the McCulloch–Pitts model provides a simple mathematical description to elaborate the interaction between presynaptic and postsynaptic neurons.

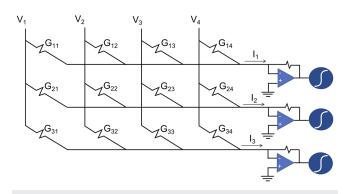

The weighted summation of the McCulloch–Pitts model can be well described in hardware by the matrix vector multiplication (MVM) in a crosspoint memory array, which is depicted in Fig. 6. In the crosspoint array, each resistive memory device is preprogrammed with conductance  $G_{ij}$ . The application of a voltage vector  $V_j$  at the array columns thus results in the generation of currents  $G_{ij}V_j$  at the memory element with coordinates (i, j) via Ohm's law. All these currents are then collected at the array rows by Kirchhoff's law, thus yielding a total row current  $I_i$  given by

$$I_i = \sum_j G_{ij} V_j, \tag{2}$$

which is inline with the argument of the activation function in Eq. (1). The output current is then typically converted into voltage by transimpedance amplifiers and passed through an activation function to fully emulate the neuronal information processing. The significant advantage of the crosspoint array circuit is that it allows us to accelerate MVM by simultaneous multiplication and summation by physical laws, in contrast with the iterative multiply accumulate (MAC) algorithm for MVM execution in digital processing units.<sup>86-88</sup> Another strong advantage is the ability to process information within the memory, thus eliminating any data transfer between the memory and the separate processing unit that

**FIG. 6.** Illustration of a crosspoint memory array to execute the MVM. The resistive memory devices playing the role of synapses are preliminarily programmed to have conductance  $G_{ij}$ . A voltage vector V<sub>j</sub> is applied to the array columns, thus resulting in output currents I<sub>i</sub> given by Eq. (2).

would be affected by the memory bottleneck of von Neumann architectures.<sup>89,90</sup> On the other hand, in-memory MVM is executed in the analog domain, which raises a number of concerns such as electronic noise, limited precision of the conductance values G<sub>ij</sub>, non-linear memory characteristics, and parasitic IR drop along the row/column lines in the array circuit.<sup>67</sup> Nonetheless, MVM has been demonstrated in several applications, such as neural network acceleration,<sup>49,91-94</sup> sparse coding,<sup>95</sup> mixed-precision computing,<sup>96</sup> compressed sensing,<sup>97</sup> solution of differential equations,<sup>98</sup> and the solution of linear matrix problems such as matrix inversion<sup>99</sup> and linear regression.<sup>100</sup>

#### A. Neuron integration

Biological neurons are also known to have a memory effect, where input spikes are integrated, instead of being summed simultaneously. The incoming signals from synapses cause the increase in a local graded potential (LGP) in the dendritic membrane. The neuron then generates an action potential if the LGP reaches a threshold; otherwise, it relaxes to its resting state if the LGP is below the threshold. The neuron can thus conduct the signal-processing functions by information integration and the threshold firing.<sup>101</sup> This functionality of the biological neuron is expressed by the concept of I-and-F neurons where spike integration causes the increase of an internal state variable, generally named membrane potential Vm. As the membrane potential reaches a given threshold V<sub>th</sub>, then the neuron responds with a fire, i.e., by sending an output spike.<sup>102,103</sup> In addition to this simple I-and-F concept, many other bio-plausible models have been proposed to implement artificial neurons, such as the leaky I-and-F model<sup>104</sup> and the biophysical HH model.<sup>105,106</sup> The I-and-F neuron is usually implemented by relatively large CMOS circuits containing tens of transistors<sup>6,107</sup> and large integrating capacitors.<sup>108</sup> For instance, a memory capacitor C<sub>mem</sub> with a capacitance of 432 fF was reported to have a layout area of 244  $\mu m^2$  in 0.35 µm CMOS technology for injection currents of the order of tens of picoamperes.<sup>108</sup> A larger capacitance may be needed in the case of larger synaptic currents, which might be the case for memorybased neural networks.<sup>109-111</sup> To reduce the circuit area for I-and-F neurons, one can take advantage of device physics of memory devices, typically in hybrid combination with CMOS transistors, to fully realize integration, firing, and bursting modes of biological neurons.

To reduce the area of the neuron integration circuit, it is possible to take advantage of pulse accumulation processes in nanoscale memory elements. For instance, the application of voltage pulses across a PCM can lead to incremental crystallization due to local Joule heating and a consequent increase in conductance, which can be used as an equivalent membrane potential.<sup>10–12</sup> Similar pulse accumulation processes in FERAM<sup>14</sup> and RRAM<sup>112–115</sup> can be used for compact spike integration, thus allowing to minimize the neuron area.

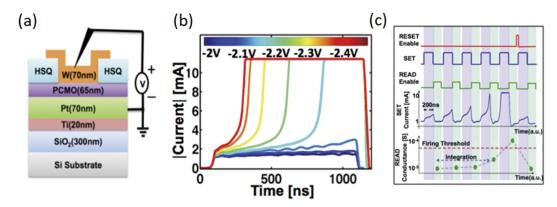

Figure 7 shows the implementation of I-and-F artificial neurons by using a  $Pr_{0.7}Ca_{0.3}MnO_3$  (PCMO) RRAM, where the integration function is performed due to the gradual conductance increase during the set process.<sup>112</sup> Figure 7(a) shows the structure of the PCMO RRAM device, where the 70 nm-thick PCMO layer is inserted between a Ti BE and a W TE. Figure 7(b) shows the measured current in response to applied pulses of fixed width and increasing

FIG. 7. I-and-F neuron based on PCMO RRAM. (a) Sketch of the RRAM device structure. (b) Time-dependent current during an applied pulse at increasing voltage amplitude. As the voltage increases, the integration phase increases its slope and the time-to-fire decreases. (c) Results of the application of voltage spikes with constant voltage. The gradual increase in current under the first four pulses indicates the integration function, while the abrupt conductance increase induced by the fifth pulse represents the fire function. Reprinted with permission from Lashkare *et al.*, IEEE Electron Device Lett. **39**, 484 (2018). Copyright 2018 IEEE.

amplitude. In general, the current shows an initial gradual increase, which can be understood as the integration phase, followed by a steep rise, representing the fire response. The non-linear current response is the result of the ion migration dynamics in PCMO, where the field-driven defect migration leads to an increase in conductance. Figure 7(c) shows the measured current in response to the application of a sequence of five voltage spikes. The conductance first gradually increases under the stimulations of repeated set pulses (i.e., integration function), followed by an abrupt increase in spike current once reaching a threshold (i.e., fire function). Subsequently, a reset pulse is used to reset the RRAM device to the initial conductance. The experimental results of current transient support the feasibility of I-and-F neurons based on PCMO RRAM.<sup>112</sup> Similarly, the neuron integration function can be performed in a SrTiO<sub>3</sub>-based memristor device with uniform switching.<sup>115</sup>

## **B.** Neuron fire

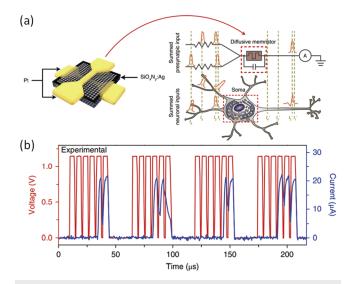

In general, devices exhibiting intrinsic threshold switching allow us to perform the fire function in a simple way, i.e., within a nanosized device instead of using bulky comparators and pulse generators. In fact, firing, bursting, and oscillating functions of the neurons have been reported by using threshold-switching devices based on Mott transition<sup>116–118</sup> and RRAM.<sup>119–123</sup> Figure 8(a) illustrates a typical implementation of an artificial I-and-F neuron, consisting of a volatile RRAM device or diffusive memristor based on SiO<sub>x</sub>N<sub>y</sub>:Ag and a parallel capacitor.<sup>120</sup> In this figure, the diffusive memristor with volatile behavior executes the fire function by threshold switching, while the capacitor conducts the integration function through the charging process. Additionally, a resistor in series with the artificial neuron is adopted as an artificial synapse and to monitor the output current vs time.

Figure 8(b) shows the experimental response of the artificial neuron to a sequence of sub-threshold stimulations.<sup>120</sup> By applying the super-threshold pulse train on the I-and-F neuron, the capacitor is charged with a typical time constant, resulting in the increase of voltage across the diffusive memristor, thus serving as the LGP state

variable. This integration process results in a negligible current during the first several pulses in the experimental data. Once the LGP reaches the threshold after a certain number of pulses, the volatile RRAM device switches to the high-conductance state, thus resulting in a fire output signal with high current. The delay time between the arrival of input spikes and the fire operation depends on the reservoir computing (RC) time constant and the internal Ag dynamics of the memristor. After fire, the device spontaneously relaxes to a low conductance state, corresponding to its resting state, as a result of the discharge of the capacitor and the volatile behavior of the RRAM device. The results in Fig. 8(b) support the feasibility of the

**FIG. 8.** The I-and-F artificial neuron comprising a SiO<sub>x</sub>N<sub>y</sub>:Ag diffusive memristor and a parallel capacitor. (a) Schematic illustration of the I-and-F neuron. (b) The experimental response of the artificial neuron. Reprinted with permission from Wang *et al.*, Nat. Electron. **1**, 137 (2018). Copyright 2018 Springer Nature.

artificial I-and-F neuron enabled by the volatile RRAM physics. Similar I-and-F neuron implementations were reported by using a vertical  $MoS_2$ /graphene threshold switching memristor.<sup>124</sup> In some cases, RRAM devices with a capacitive effect, referred to as mem-capacitors, are also used to replace the common capacitor to implement the I-and-F neurons.<sup>125–127</sup> For instance, I-and-F neurons with various neuron functions were reported using single RRAM devices based on GaTa<sub>4</sub>Se<sub>8</sub><sup>128</sup> and a stack of Ag/FeO<sub>x</sub>/Pt.<sup>129</sup> The combination of I-and-F functions in nanoscale memory devices is most promising to improve the scalability of artificial spiking neurons.

## C. Oscillating neurons

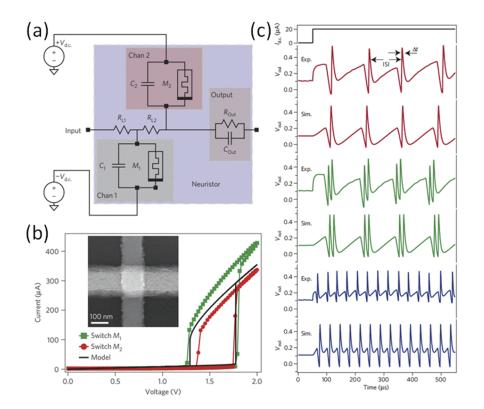

Threshold switching in volatile RRAM devices provides the basis for generating self-sustained oscillations, thus enabling bioplausible artificial neurons. Figure 9 illustrates an oscillating neuron based on the Mott insulator NbO<sub>2</sub>.<sup>116</sup> As shown in Fig. 9(a), the application of a voltage close to a characteristic threshold voltage  $V_T$  causes the NbO<sub>2</sub> layer to switch from a high-resistance (off) state to a low-resistance (on) state, followed by a fast recovery of the initial off state. This threshold switching effect was explained due to internal Joule heating triggering a higher conductance due to Poole Frenkel transport<sup>130-133</sup> or insulator–metal transition typical of Mott insulators<sup>134</sup> or by a coexistence of these phenomena.<sup>135</sup> To describe the complex dynamics of Na<sup>+</sup> and K<sup>+</sup> ion channels in the HH neuron model, two elements are used in the HH neuron circuit of Fig. 9(b) each including a parallel combination of a NbO<sub>2</sub> RRAM device and a capacitor. These two ionic channels are stimulated by

pulses with opposite polarity bias and coupled to each other by the load resistor RL2, while the load resistor RL1 serves as input resistance. The parallel combination of the threshold switching device and a capacitor is able to induce oscillatory spike trains with various shapes. Assuming a constant input current, a time-oscillating response can be obtained by the HH circuit. Figure 9(c) shows experimental results of the output of the HH neuron circuit, compared to circuit simulations for a constant input current of 20  $\mu$ A. The inter-spike time interval can be controlled by the value of capacitances C1 and C2. Similar oscillatory HH neurons have been developed based on other types of devices exhibiting threshold switching, such as other Mott insulators  $VO_2^{136}$  and  $TaO_x^{137}$  and chalcogenide glass GeSe.<sup>13</sup> Oscillatory neurons have also been demonstrated by using SiO<sub>x</sub>N<sub>y</sub>:Ag volatile RRAM, which is capable of controlling the oscillation frequency by the conductance value.<sup>138</sup> Threshold switching in a HfO2 layer with the Pt/Ag nanodot top electrode and Pt bottom electrode was reported to display low operation voltage (<0.6 V) and ultralow power consumption  $(<1.8 \mu\text{W})$ , thus enabling low voltage/low power oscillatory neurons.123

## D. Dendritic filtering

In the biological nervous system, dendrites are important components of neuronal units that extend from the cell body of neurons and play a critical role in information processing.<sup>139–141</sup> Dendrites are generally considered to be passive elements that merely transmit synaptic currents to the soma. They can integrate synaptic inputs and output signals nonlinearly and filter

FIG. 9. Implementation of an oscillatory neuron using a HH model. (a) Schematic of the HH neuron circuit comprising two RRAM devices based on the Mott insulator NbO<sub>2</sub> (M1 and M2) and two parallel capacitors ( $C_1$  and  $C_2$ ). (b) The I–V curve and the typical SEM image of the NbO<sub>2</sub> memristor. (c) Spike burst and trains of the oscillatory neuron. Reprinted with permission from M. D. Pickett, G. Medeiros-Ribeiro, and R. S. Williams, Nat. Mater. **12**, 114 (2013). Copyright 2013 Springer Nature.

out insignificant background information.<sup>142–144</sup> Recently, several CMOS-based circuits have been reported to emulate the dendrite functions.<sup>145,146</sup> Implementing the dendrite function in nanoscaled devices is thus highly desirable for neuromorphic engineering. Dendritic integration was shown by using starch-based electrolyte-gated oxide transistors.<sup>147</sup> Spatiotemporal dendritic integration and linear/superlinear dendritic algorithms were demonstrated within transistor structures.<sup>148,149</sup>

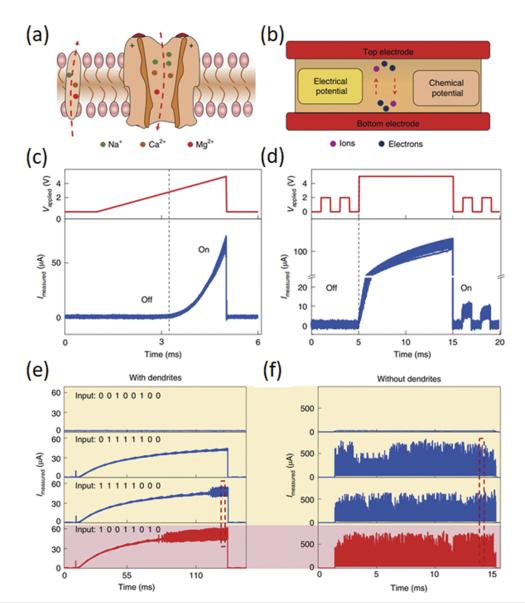

provides the foundation to implement the key dendritic functions.<sup>150</sup> To implement dendritic nonlinear integration and filtering functions, a volatile RRAM with Pt/TaO<sub>x</sub>/AlO<sub>δ</sub>/Al stack was proposed, where a positive voltage stimulus leads to conductance increase followed by a gradual relaxation to the initial high-resistance state as the voltage bias is removed. Figure 10(c) shows the measured electric characteristics of the artificial dendritic device, indicating a nonlinear current response to a linearly increasing voltage from 0 to 5 V, which is similar to that of N-methyl-d-aspartate (NMDA) channels in the biological dendrite. Figure 10(d) shows that the RRAM

Figure 10 illustrates the analogy between the ionic channel in a biological synapse (a) and the two-terminal RRAM device (b), which

FIG. 10. Illustration of artificial dendrites by RRAM devices. (a) Schematic of the membrane of a biological dendrite. (b) A metal–oxide-based dynamic memristor as an artificial dendrite. (c) Measured nonlinear current response to the applied voltage on the fabricated artificial dendrite. The applied voltage ramped linearly from 0 to 5 V. (d) Measured current response of the artificial dendrite device in the off and on states, exhibiting a nonlinear filtering and integration property. (e) Measured output current of the neural network with artificial dendrites for different input patterns. (f) Measured output current of the neural network without artificial dendrites for different input patterns. Reprinted with permission from Li *et al.*, Nat. Nanotechnol. **15**, 776 (2020). Copyright 2020 Springer Nature.

device can filter out sub-threshold input signals smaller than the threshold of 3 V and performs nonlinear integration of input signals larger than the threshold voltage, resulting in a continuously increasing current response over time. The filtering effect can be explained by the energy barrier for oxygen ion migration. Only the input signals with amplitude larger than the threshold voltage can induce the oxygen ion migration toward the Al electrode, resulting in a decrease in the barrier height and an increasing current response to the applied voltages. On the other hand, the sub-threshold input signals are filtered out. Figures 10(e) and 10(f) shows the measured current during the inference process of a neural network for various input patterns with and without artificial dendrites, respectively. The pattern recognition accuracy and power consumption are significantly improved by including the dendritic devices into the neural network, thanks to the filtering effect.

# V. HARDWARE SYNAPSES

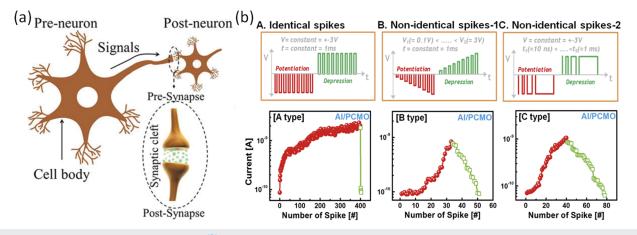

Synapses in the biological neural system are responsible for the weighted transmission of spikes from a pre-synaptic neuron to a post-synaptic neuron, as depicted in Fig. 11(a).<sup>151</sup> Most importantly, the synaptic weight should be able to adjust depending on the history of spiking stimulation, a phenomenon known as synaptic plasticity that is regarded as the basis for learning and memory functions. Synaptic plasticity can be realized in hardware via the conductance change in memory device, such as the set and reset processes in RRAM devices that have been widely developed to mimicking biological synapse.<sup>151-155</sup> The close emulation of synaptic functions is a critical step to achieve a neuromorphic system with the ability to learn and adapt in response to environmental changes. Generally, the synaptic plasticity can be categorized into long-term plasticity and short-term plasticity depending on the retention time, representing the permanent and temporary synaptic modification, respectively<sup>47,155,156</sup> Various long- and short-term synaptic functions have been demonstrated by utilizing memory devices, such as STDP, spike-rate-dependent plasticity (SRDP), paired-pulse facilitation (PPF), and paired-pulse depression (PPD). 47,151-159

#### A. Long-term potentiation and depression

Long-term potentiation (LTP) and long-term depression (LTD) consist of the permanent increase or decrease, respectively, in the synaptic weight as a result of the spiking stimulation. LTP and LTD are possible in nonvolatile memory devices by the pulseinduced change of the conductance according to the input pulse shape and number.<sup>155</sup> Both digital (binary) and analog (multilevel) conductance change are reported.<sup>160–162</sup> Binary states are more suitable for memory storage due to the clear difference between highresistance state (HRS) and low-resistance state (LRS).<sup>163</sup> On the other hand, analog states are ideal for synaptic devices with incremental weight update.<sup>151–155</sup> In particular, analog-type conductance states with linear and symmetric LTP/LTD are essential in hardware accelerators of inference and training.<sup>49,93,94,164-166</sup> Non-linear and asymmetric LTP/LTD are commonly observed in most synaptic devices.<sup>67,94,167</sup> Algorithmic and engineering methods should be identified to compensate the intrinsic linearity of synaptic weight update.

The linearity of the update characteristics can be improved by optimization of the programming pulse,<sup>168</sup> utilization of defects engineering,<sup>169</sup> and adoption of three terminal devices such as the ECRAM.<sup>68,74</sup> Figure 11(b) shows the LTP and LTD behaviors of a Pr<sub>0.7</sub>Ca<sub>0.3</sub>MnO<sub>3</sub> (PCMO) based memristor under the programming spikes with different pulse schemes.<sup>168</sup> The A-type behavior is a typical update characteristic with nonlinear LTP and abrupt LTD, which was obtained by using spikes with constant voltage amplitude. The update linearity of LTP/LTD can be clearly improved by adopting spikes with incremental amplitude (type B) and pulse width (type C). These results indicate that non-identical pulses are most effective in controlling and improving the synaptic update linearity. This is because the increasing amplitude/pulse-width compensates the typical saturating behavior of the conductance for constant pulses.<sup>94</sup> However, note that the increasing amplitude and increasing width

19 September 2024 09:43:18

methodologies are not compatible with the outer product scheme of weight update, where the whole crosspoint array is updated simultaneously by applying voltage vectors at the rows and columns with variable pulse widths.<sup>169</sup> The increasing amplitude and width thus results in more complicated updated schemes requiring longer update time and larger energy consumption.

The LTP/LTD linearity can be also enhanced in ECRAM devices, thanks to the bulk-type of switching and to the separation between the programming path (between the gate and channel) and the read path (across the channel between the source and drain). This allows for better controllability of the device conductance by field-induced migration of impurities, such as Li ions in inorganic ECRAM.<sup>68–70</sup> or protons in organic ECRAM.<sup>71</sup>

## B. Spike-timing-dependent plasticity (STDP)

STDP, namely, the weight modification relying on the temporal order of pre- and post-synaptic spikes, is regarded as one of the essential learning rules for unsupervised learning.<sup>7,9,154,155</sup> Thus, implementing STDP rules in hardware SNNs is a critical step toward achieving neuromorphic systems capable of learning and adaptation. For the typical STDP rule, the synaptic weight undergoes LTP if a pre-synaptic spike occurs earlier than a post-synaptic spike, i.e., if the spike delay  $\Delta t = t_{post} - t_{pre}$  between the post-synaptic spike time  $t_{post}$  and the pre-synaptic spike time  $t_{pre}$  is positive. Conversely, LTD takes place for the case  $\Delta t < 0$ .<sup>154,155</sup> To achieve the above STDP function, the synaptic device usually needs to satisfy the requirement of gradual conductance change and fast response to individual spikes.

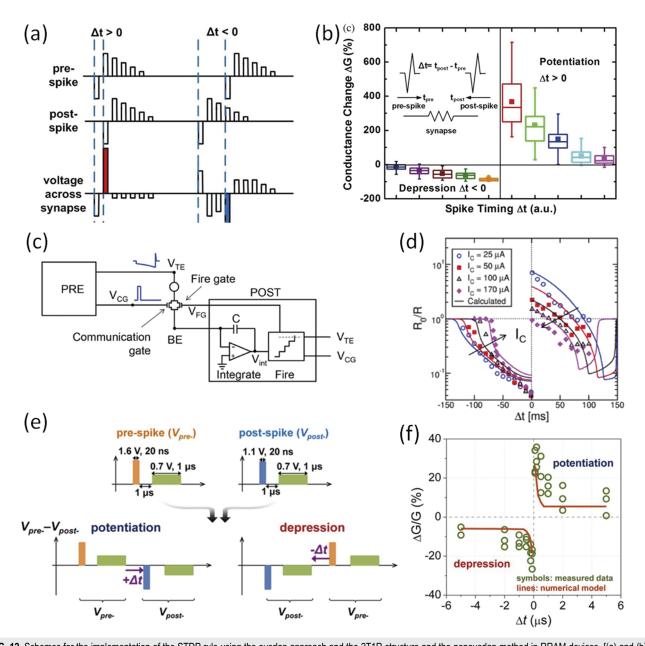

Various STDP methods have been reported for both digitaland analog-type memory devices.<sup>154,155,170-173</sup> A typical approach for STDP is the overlap method where the neuron spike is designed such that the  $\Delta t$ -dependent overlap between pre- and post-synaptic spikes leads to the desired LTP or LTD.<sup>154,172,173</sup> Figure 12 shows typical examples of overlap-type implementations of STDP for HfO2-based RRAMs.<sup>173,174</sup> The pre- and post-spikes can be designed as series of six pulses, where the first negative pulse is followed by five positive pulses with decreasing amplitude, as shown in Fig. 12(a). An important design principle is that each individual spike is unable to induce a conductance change  $\Delta G$ , i.e., all pulses should be below the threshold for set/reset processes. However, the overlap between the pre-spike applied at one electrode and the post-spike applied at the other electrode causes a voltage drop across the memory device that is large enough to change the conductance. As illustrated in Fig. 12(a), when the pre-spike is applied earlier than the post-spike  $(\Delta t > 0)$ , the overlapping spikes result in a positive pulse with a relatively large amplitude, hence LTP.<sup>173</sup> On the other hand, for  $\Delta t < 0$ , the overlapping spikes cause a negative pulse with large amplitude, hence LTD. Most importantly,  $\Delta t$  controls the amplitude of the resulting pulse amplitude, hence the degree of conductance change  $\Delta G$ . Figure 12(b) shows the measured  $\Delta G$  as a function of the spike timing, indicating that the amplitude of positive and negative  $\Delta G$  decreases for increasing delay  $|\Delta t|$ , in agreement with the STDP rule.<sup>173</sup> Previous work suggests that the correlation between  $\Delta G$  and  $\Delta t$  can be tuned by adjusting the pulse shape and the programming scheme.<sup>175</sup> Various types of STDP curves were obtained by the overlap approach in various synaptic devices, including RRAM,<sup>1</sup> PCM,<sup>178-180</sup> MRAM,<sup>181</sup> and FERAM.<sup>182</sup>

The overlap STDP scheme may suffer from a relatively large variation of  $\Delta G$ , since there is no compliance current to control the growth of the conducting filament during the LTP process. To overcome this issue, the two-transistor/one-resistor (2T1R) synaptic circuit structure was proposed to implement the STDP function in RRAM<sup>174</sup> and PCM.<sup>183</sup> As shown in Fig. 2, a series MOS transistor can limit the current during the set transition for better controlling the resistance in RRAM.<sup>35,184</sup> The additional transistor also provides a multiple-input control for handling the various synaptic functions, i.e., spike transmission, LTP, and LTD. Figure 12(c) illustrates the 2T1R synapse, where the PRE spike is applied to the RRAM TE, while the POST spike is applied to the fire gate (FG). Additionally, a short positive pulse is given to the communication gate (CG) of the second transistor for synaptic transmission. The coincidence of the PRE spike with amplitude V<sub>TE</sub> and the POST spike with amplitude of V<sub>FG</sub> can induce the set and reset transition of resistive switching memory, thus leading to LTP and LTD, respectively. Importantly, the filament growth is controlled by the V<sub>FG</sub>, which, in turn, depends on the spike timing, thus enabling time-dependent potentiation according to the STDP function. Figure 12(d) shows the resulting STDP characteristics, namely, the relative change of conductance  $R_0/R$ , where  $R_0$  is the resistance before the spike application and R is the final resistance, for various initial states R<sub>0</sub> obtained for various I<sub>C</sub>. The results indicate LTD for  $\Delta t < 0$  and LTP for  $\Delta t > 0$ , where the change of conductance tends to vanish at increasing  $|\Delta t|$ , which is in line with the observed biological STDP.7 A simplified STDP synaptic circuit was reported by adopting a one-transistor/oneresistor (1T1R) structure with the RRAM synapse.<sup>111,185</sup> This was later extended to a four-transistor/one-resistor (4T1R) structure to demonstrate the SRDP.<sup>186,187</sup>

Although the overlap method allows for the efficient STDP function with local activity, it does not fully account for the observed biological STDP, where overlapping spikes are generally not necessary for weight update. To overcome this limitation, the secondorder memristor was proposed to execute LTP/LTD according to the STDP rule without any overlap between pre- and post-spikes.<sup>18</sup> The second-order memristor consists of a RRAM device where the conductance change is not only determined by the first variable, e.g., the filament size or interface barrier, but also by a second variable, e.g., the local temperature or oxygen mobility, which impacts the dynamics of the first variable.41,155,188,189 The second variable usually displays a transient dynamics, such as a spontaneous decay after stimulation, which is similar to the  $Ca^{2+}$  dynamics in the biological synapse. As a result, the second-order memristor can display non-overlap, biorealistic emulation of STDP rule and other synaptic learning functions.<sup>41,155,188,189</sup> Figure 12(e) illustrates the pre-/post-spikes, including a programming pulse with high amplitude and a heating pulse with long pulse width. By applying the pre- and post-spikes at the TE and BE, the interaction between the applied electric field and the local temperature can lead to a  $\Delta$ t-dependent conductance change, as indicated by the STDP characteristic for a Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>y</sub> second-order memristor in Fig. 12(g). Similarly, a second-order memristor consisting of a Pt/WO<sub>3-x</sub>/W stack was reported, where the two variables are the Schottky barrier and the oxygen ion mobility.<sup>177</sup> Second-order memristors were experimentally demonstrated for various material systems, such as InGaZnO,<sup>155</sup>  $Ta_2O_{5-x}/TaO_{y}$ ,<sup>188</sup>  $WO_{3-x}$ ,<sup>177,189</sup> SrTiO<sub>3</sub>,<sup>190</sup> SiO<sub>x</sub>N<sub>v</sub>:Ag,<sup>41</sup> and TiO<sub>2</sub>:Ag.<sup>191</sup>

19 September 2024 09:43:18

**FIG. 12.** Schemes for the implementation of the STDP rule using the overlap approach and the 2T1R structure and the nonoverlap method in RRAM devices. [(a) and (b)] The pulse design and measured STDP of the HfO<sub>2</sub>-based RRAM through overlapping the pre- and post-spikes.<sup>173</sup> (c) The illustrative scheme for 2T1R synapse containing a memristor and two transistors. (d) The tunable STDP curves with different initial conductance states obtained by setting the device under increasing I<sub>C</sub> from 25 to 170  $\mu$ A.<sup>174</sup> [(e) and (f)] The operation design and the realization of the STDP function using the nonoverlap spikes in a second-order Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>y</sub> memristor.<sup>188</sup> Reprinted with permission from Yu *et al.*, IEEE Trans. Electron Devices **58**, 2729 (2011). Copyright 2011 IEEE; Wang *et al.*, Front. Neurosci. **8**, 438 (2015). Copyright 2015 Frontiers; and Kim *et al.*, Nano Lett. **15**, 2203 (2015). Copyright 2015 ACS.

## C. Spike-rate-dependent plasticity (SRDP)

In the human brain, there are two main types of information coding, namely, time coding and rate coding. While STDP is most suitable for learning in the presence of time coding, SRDP can serve as the learning rule for rate coding.<sup>192</sup> Frequency dependent LTP/LTD have been extensively reported in memory devices with dynamic effects, e.g., oxygen diffusion.<sup>193,194</sup> SRDP generally relies on the Bienenstock–Cooper–Munro (BCM) learning rule as a high-order function of SRDP.<sup>195–197</sup> According to the BCM rule,

spike trains with a frequency larger than a certain threshold induce LTP, while spike trains with a lower frequency lead to LTD. A threshold slide effect has been reported, where the threshold frequency changes depending on the learning experience, thus enabling a history-dependent synaptic adaptation.<sup>83,198</sup> Many efforts have been made to realize the BCM rule by using the rate-based prespikes in the second-order memristors.<sup>189,199</sup> In these schemes, the

forgetting effect of the learning experiences and the potentiation effect induced by the rate-based pre-spikes were compared, thus achieving the BCM learning rule with the monotonic trend. The effect of tunable forgetting rate on the BCM curve was studied for SrTiO<sub>3</sub>-based RRAM devices.<sup>200</sup> However, monotonic SRDP is not consistent with the "tick" shape of the BCM rule in biological systems. In addition, the BCM rule should represent the long-term

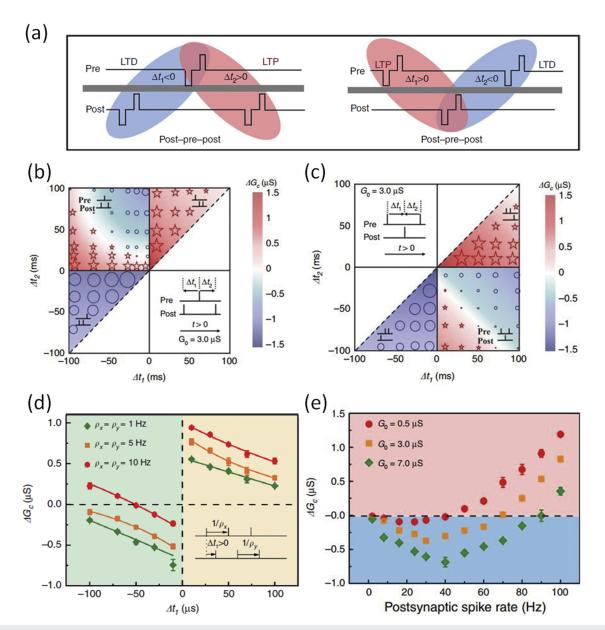

**FIG. 13.** Bio-realistic demonstration of the BCM learning rule using a triplet-STDP scheme.<sup>199</sup> (a) Scheme for the typical spike triplets of "post–pre–post" and "pre–post–pre." [(b) and (c)] The experimental results of triplet-STDP measured in the WO<sub>3-x</sub> memristor. It summarized the LTP and LTD using the sequences of "post–pre–post" and "pre–post–pre" with various timing intervals. The degree of  $\Delta G$  is indicated by both the symbol size and background color. (d) The dependence of  $\Delta G$  on both the pre-spike rate  $\rho_x$  and post-spike rate  $\rho_y$ . (e) The triplet-STDP based BCM rules with various learning experiences (i.e., different initial conductance G<sub>0</sub>). Reprinted with permission from Wang *et al.*, Nat. Commun. **11**, 1510 (2020). Copyright 2020 Springer Nature.

characteristics rather than the short-term modification implemented in some studies.  $^{189,200}$

Compared to the standard STDP with paired spikes, a third spike is introduced in the triplet-STDP, thus resulting in a triplet of interacting spikes. The interaction of paired spikes with the third spike leads to the multiplicative term to enable the BCM rule. In biological systems, there are two types of triplet STDP, namely, the first-spike-dominating rule and last-spike-dominating rule. The former was demonstrated in a Pt/SrTiO<sub>3</sub>/Nb-STO stack RRAM exhibiting synaptic suppression triplet-STDP.<sup>115</sup> Last-spikedominating triplet-STDP was reported for a Pt/WO<sub>3-x</sub>/W secondorder memristor.<sup>199,201</sup> This is shown in Fig. 13(a) reporting the typical triplets of "post-pre-post" and "pre-post-pre" for stimulating the WO<sub>3-x</sub> synaptic RRAM device. Figure 13(b) shows the conductance change as a function of the first and the second spike delay in the post-pre-post triplet,  $\Delta t_1$  and  $\Delta t_2$ , respectively, while Fig. 13(c) shows the same for the pre-post-pre triplet. Figure 13(d) shows the measured  $\Delta G$  as a function of  $\Delta t_1$  for increasing spiking rate, indicating that plasticity depends on both the pre-spike rate  $\rho_x$  and post-spike rate  $\rho_y$ . Based on these results, the BCM learning rule can be implemented by designing a proper triplet-STDP scheme. Figure 13(e) illustrates the triplet-based BCM learning rule by extracting the data from the diagonal line of quadrant II in Fig. 13(b) and defining the post-spike rate as given by  $\rho_{\rm y} = 1/(|\Delta t_1| + |\Delta t_2|)$ . The experience-dependent sliding threshold characteristic is also demonstrated by tuning the initial conductance G<sub>0</sub> in such BCM implementation, resulting in a close emulation of the biological BCM curve.199

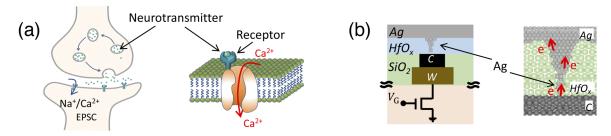

## D. Short-term synaptic plasticity and memory

While long-term plasticity can last for the entire lifetime, shortterm plasticity or short-term memory (STM) in the human brain can be as short as milliseconds to minutes.<sup>148–150</sup> Several typical types of STM have been realized in hardware memory devices, including the excitatory postsynaptic current (EPSC), PPF/PPD, and SRDP.<sup>47,155–157,193,194</sup> Usually, STM is implemented by directly taking advantage of the inherent transient behavior of volatile memory devices. For instance, Fig. 14 shows the analogy between the transient dynamics of the EPSC<sup>202</sup> and the volatile nature of an Ag filament in an HfO<sub>2</sub>-based RRAM device.<sup>203</sup> In a biological synapse of Fig. 14(a), a pre-synaptic spiking stimulation induces the release of a neurotransmitter from synaptic vesicles into the synaptic cleft. The neurotransmitter, e.g., L-glutamate, then binds to the receptor to activate an ion channel, thus triggering the ionic inflow of Na<sup>+</sup> and Ca<sup>2+</sup> into the post-synaptic neuron, which is responsible for the EPSC.<sup>202</sup> The opening of the ion channels has limited duration in time, which accounts for the transient nature of the EPSC. In a volatile RRAM, the electrical pulse results in the formation of an Ag filament, which then serves as a conductive bridge for electrons across the RRAM. Both the EPSC and the conductive filament remain active for a short time, typically in the range from few ms to several minutes. The physics of the volatile RRAM can thus serve as a basis for replicating STM in hardware via a small-scale device, i.e., without the need for large capacitors to emulate relatively long time constants.

Volatile memory effects have been used to naturally emulate the EPSC in several two- and three-terminal memory devices.<sup>41,155,204–207</sup> Similarly, volatile memory devices can also mimic the PPF induced by paired spikes.<sup>204–207</sup> In a biological PPF, the second spike can generate much larger change of synaptic weight than the first spike, thus resulting in a strong spike interaction and correlation of spikes in the Ca<sup>2+</sup> dynamics. On the other hand, paired spikes may also cause synaptic depression, hence PPD, which has been also mimicked in several memory devices.<sup>157,208,209</sup>

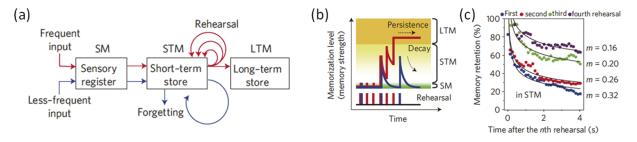

According to our daily experience, it is known that STM is capable to transition to long-term memory (LTM) by repeated training, as illustrated in Fig. 15(a).<sup>47</sup> Ag<sub>2</sub>S-based volatile RRAM, also called atomic switches, can replicate a similar function. Figure 15(b) depicts a simplified memory model to implement the transition from STM to LTM transition in a volatile RRAM synapse, where the memorization level can increase from the sensory memory (SM) to STM and LTM by increasing the number of stimulations, similar to repeated rehearsals in the human experience. Figure 15(c) shows that data retention is clearly enhanced by repeated stimulations, supporting the transition from STM to LTM in the Ag<sub>2</sub>S RRAM device. Similar to the Ag<sub>2</sub>S RRAM device, the transition from STM to LTM has been extensively reported for various memory devices. <sup>155,156,210,211</sup>

# E. Cognitive computing functions enabled by STM

STM is an essential function in the human brain that is functional for several sensing and recognition functions, such as the

**FIG. 14.** Analogy between EPSC in biological synapses and the diffusive Ag filament in volatile RRAM devices. (a) The pre-synaptic stimulation causes the release of a neurotransmitter, which activates Ca<sup>2+</sup> transport across the ionic channels at the basis of EPSC. (b) An Ag filament is formed by a voltage pulse via Ag ion migration. The Ag filament then serves as a bridge for electron conduction across the Ag filament. Reprinted with permission from R. A. Lester and C. E. Jahr, J. Neurosci. **12**, 635 (1992). Copyright 1992 The Society for Neuroscience and Wang *et al.*, Adv. Intell. Syst. **3**, 2000224 (2020). Copyright 2020 Wiley.

**FIG. 15.** Illustration of the transition from STM to LTM in volatile RRAM devices.<sup>47</sup> (a) The psychological model of human memory and (b) the simplified memory model for RRAM synapse. (c) The STM-to-LTM transition with repeated learning in the Ag<sub>2</sub>S-based atomic switching memristor. Reprinted with permission from Ohno *et al.*, Nat. Mater. **10**, 591 (2011). Copyright 2011 Springer Nature.

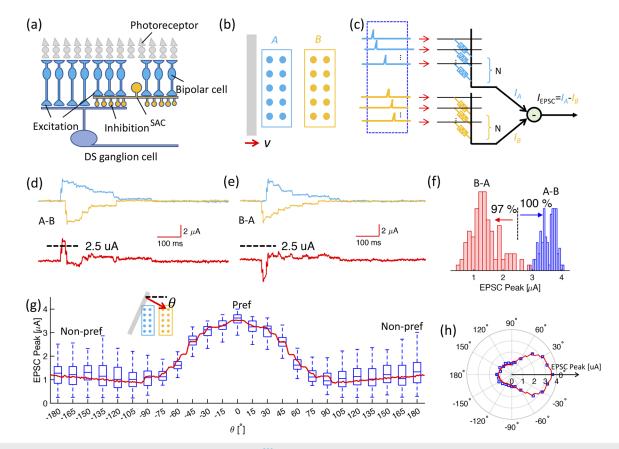

recognition of speech, movement, and other types of dynamic information. Figure 16 shows an example of the use of volatile RRAM for the movement recognition and direction selectivity similar to the human retina. The biological visual system is capable of fast motion detection by direction-selective (DS) ganglion cells.<sup>212</sup> As shown in Fig. 16(a), the retina includes bipolar cells and starburst amacrine cells (SACs) with receptive fields capable of stimulating the ganglion cells with excitatory and inhibitory inputs, respectively.<sup>203</sup> The combination of excitatory and inhibitory signals causes an EPSC into the ganglion cells, which enables the recognition of various moving directions under sight. Figure 16(b) shows receptive field stimulated by a moving light bar, which first induces excitatory

FIG. 16. Illustration of movement recognition by volatile RRAM devices.<sup>203</sup> (a) Structure of the direction-selective (DS) ganglion cell, comparing excitatory and inhibitory EPSCs induced by light-stimulated photoreceptors [(b) and (c)] The movement of a light bar across the receptive field causes the activation of excitatory current spikes, followed by inhibitory current spikes, which result in an EPSC with large positive current. [(d) and (e)] Comparison of excitatory and inhibitory currents from volatile RRAM devices for the case of an image bar moving from left to right (preferred direction) and from right to left (non-preferred direction). Only the EPSC of the preferred direction can exceed the threshold, thus being recognized. (f) Histogram of EPSC for preferred and non-preferred directions. [(g) and (h)] EPSC peak as a function of the movement direction over the whole range of angles. Reprinted with permission from Wang *et al.*, Adv. Intell. Syst. **3**, 2000224 (2020). Copyright 2020 Wiley.

current spikes, followed by inhibitory current spikes. The comparison between the transient excitatory and inhibitory currents results in an EPSC with large positive current, which exceeds a threshold, thus triggering the detection of the preferred direction. The transient excitatory and inhibitory currents were replicated in hardware by volatile RRAM with Ag TE and HfO<sub>2</sub> as the switching material.<sup>203</sup> Figure 16(c) schematically shows the circuit with several volatile RRAM to enable the averaging of stochastic excitatory and inhibitory currents. The overall EPSC, obtained as the subtraction of excitatory and inhibitory currents, shows a positive peak for the preferred direction [left to right, Fig. 16(d)] and negative peak for the non-preferred direction [right to left, Fig. 16(e)]. Figure 16(f) shows the distribution of preferred and non-preferred EPSCs, indicating that the two directions can be efficiently discriminated by comparing the EPSC to a threshold. The same concept can be extended to the full range of movement directions [Figs. 16(g) and 16(h)], thus enabling fast direction sensitivity by direct current sensing in the analog domain.<sup>203</sup>

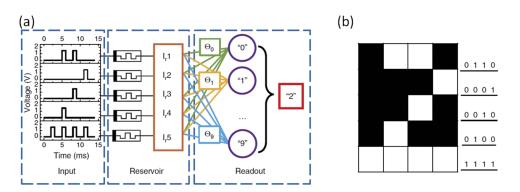

STM is also at the basis of reservoir computing (RC) systems,<sup>214,215</sup> which are widely utilized to implement temporal and sequential data processing. Generally, a RC system consists of a reservoir network for mapping the input stimuli into a highdimensional feature space and a readout network for the analysis of the response from the reservoir states and final inference. Volatile memory devices with intrinsic STM behavior offer an ideal platform for brain-inspired implementing RC systems. For instance, volatile WOx-based RRAM with the STM dynamic effect was used to implement a RC network for image recognition.<sup>213</sup> Figure 17 shows the network architecture of the RC system for digit recognition using five volatile RRAM devices. Each digit is mapped into 20 pixels, as shown in Fig. 17(b) for the case of digit 2. The 20 pixels are divided into five rows, each row stimulated with a sequence of four consecutive spikes applied to one of the five RRAM synapses. As a result, each RRAM device is stimulated by a four-spike timeframe input stream. The image is thus represented by a spatiotemporal coding, i.e., not only using the spatial location in the rows but also the temporal sequence of the stream. For the readout function, a fully connected network with five input neurons and ten output neurons is employed to measure the conductance states of the five memristors

in the reservoir network and recognize the digit. The recognition of the ten digits is executed only using five memristors, which is far less than the 200 weights in a conventional neural network. Similar spatiotemporal RC networks based on RRAM have been shown for handwritten digit recognition,<sup>213</sup> solution of second-order non-linear tasks,<sup>213</sup> spoken-digit recognition,<sup>214</sup> and autonomous chaotic time-series forecasting.<sup>214</sup> Besides top-down memory devices fabricated with conventional microelectronic technology, bottom-up approaches have been proposed. For instance, volatile switching was demonstrated in a network of switching nanowires capable of learning via homo-synaptic and hetero-synaptic plasticity.<sup>216</sup> This concept might pave the way for hardware implementation of unconventional computing paradigms in self-organizing stochastic networks of nanowires.

## VI. TECHNOLOGICAL CHALLENGES AND POTENTIAL SOLUTIONS

While RRAM devices offer a wealth of physical properties that are attractive for neuromorphic computing primitives, there are several technological challenges that currently prevent the widespread adoption of RRAM for memory and computing.

A major technological limitation is given by the programming and read variations that prevent repeatable, reliable storage of data. This is a strong issue especially for multilevel storage where the drift and fluctuation of the conductance cause time-dependent retention failure.<sup>51</sup> For instance, deep neural networks (DNNs) adopting multilevel weights for MVM are heavily affected by fluctuations and drift that can cause a significant drop of accuracy during time. 49,217 Programming variations can be mitigated by accurate program-verify algorithms based on voltage- or current-ramping during the set or reset operation. In particular, current-based approaches appear most promising, thanks to a relatively shallow programming characteristics, compared to voltage-based techniques.<sup>218</sup> Relaxation effects might be mitigated by redundancy techniques, where averaging among various devices allows for a better robustness toward individual fluctuations and noise.<sup>219</sup> It has been observed that low-current LRS is more affected by drift and variations after programming, as a result of the smaller size of the conductive filament.<sup>220</sup> Therefore,

FIG. 17. Illustration of reservoir computing enabled by STM. (a) Network for digit recognition based on the memristive reservoir computing system. (b) Image pattern for digit "2," based on five memristors each receiving a sequence of four spikes. Reprinted with permission from Du *et al.*, Nat. Commun. 8, 2204 (2017). Copyright 2017 Springer Nature.

one may configure the network algorithm in such a way that the number of intermediate weights is minimized, whereas the presence of HRS and full LRS with high stability is maximized.<sup>221</sup> RRAM technologies with higher stability, such as epitaxial<sup>63</sup> and uniform switching RRAM,<sup>64–66</sup> might also improve the immunity to resistance fluctuations for high precision in-memory computing. On the other hand, neuromorphic computing appears less affected by variations and stochasticity, thanks to the self-adaptation and continuous learning, where a change in the device parameters can be compensated in real time. However, note that variability in neuromorphic circuits does not only affect the synaptic weight but also all other brain-inspired properties such as neuron integration and retention time of short-term synapses.

Another key issue for RRAM is the excessive read current, which is due to the filamentary conduction across a metallic path with nanometric length in the active oxide. Typically, the LRS shows a conductance in the range between 10 and 100 k $\Omega$ , which corresponds to a synaptic current between 1 and 10  $\mu$ A for a typical read voltage of 0.1 V. While this current is reasonable for typical memory applications, aimed at fast read in the presence of large parasitic capacitances within large arrays, it represents a critical limitation for MVM implementations in DNNs and other neuromorphic applications. For instance, assuming a crosspoint array of size 128 × 128 in Fig. 6 with an average synaptic current of  $I_{read} = 10 \,\mu$ A, the current in an individual row/column would reach 640 µA, assuming 50% probabilities of HRS and LRS, which requires a decoder transistor with the proper channel size for sensing and amplification. In addition, the large read current may lead to a significant voltage drop, also known as IR drop, along the row/columns of the crosspoint array. For instance, assuming a cell-to-cell wire resistance of  $r = 1 \Omega$  in the array columns/rows,<sup>222</sup> the total voltage drop would be approximately given by  $\Delta V \approx rI_{read}N^2/2$ , which gives  $\Delta V \approx 82$  mV, thus contributing to an error around 82% with respect to the applied voltage. Reducing the operating current in the device typically requires LRS at a relatively small filament size, which is, in turn, less stable with respect to drift and fluctuations. At the architecture level, the IR drop issue is addressed by adopting crosspoint arrays, also referred to as tiles, with a relatively small size, e.g., in the  $32 \times 32$  range.<sup>223</sup> Sparsity, which is typical of the human brain, hence of many hardware neuromorphic circuits, can alleviate the IR-drop problem, as it reduces the number of active synapses within the array. Alternative device concepts, such as uniform switching RRAM<sup>64-66</sup> or ECRAM<sup>67-74</sup> characterized by bulk-type conduction, appear more promising in reducing the read current, thus enabling a larger size of the neuromorphic array.

More on the technological side, provided that synaptic currents can be substantially reduced, a significant issue is the development of a high density crosspoint array, possibly with 3D integration. The brain is, in fact, characterized by a high connectivity, where each neuron is connected, on average, to 10 000 neurons.<sup>224</sup> Achieving such a large connectivity thus requires arrays with extremely large numbers of rows and columns, which makes 3D integration mandatory to fit the neuromorphic circuit within a single chip. Recently, 3D crosspoint arrays with eight layers of RRAM devices with vertically aligned electrode have been demonstrated for DNN implementation,<sup>27</sup> although the extension of this technology to brain-inspired cognitive circuits has not been reported yet. In this regard, a significant challenge is the RRAM selector, since the

3D integration of CMOS transistors is not straightforward. Several non-linear selectors with the capability of 3D integration have been reported, including Mott insulator,<sup>225–227</sup> chalcogenide glasses,<sup>228,229</sup> mixed ion-electron conduction (MIEC) devices,<sup>230</sup> multilayer tunnel junctions,<sup>231</sup> and threshold vacuum switches.<sup>232</sup> The resulting one-selector/one-resistor (1S1R) structure is extremely compact and suitable for 3D integration, thus being very attractive for both memory<sup>233</sup> and computing applications.<sup>67</sup> 3D-integrated, monolithic circuits capable of hetero-integration of various RRAM technologies, each serving a different function for sensing, neurons and synapses, would provide the ideal technology platform for the neuromorphic system capable of paralleling the brain computing functionality via device physics.

## **VII. CONCLUSIONS**

Neuromorphic computing requires a set of ad hoc hardware capable of harnessing device physics to recreate the neuron and synapse functions in the human brain. RRAM offers a range of physical phenomena, arising from electrical transport, switching, and ion migration, that can be used to approximate neuromorphic functions, such as neuronal integration, fire, oscillations, dendritic filtering, and synaptic plasticity according to various spike-time and spikerate learning rules experimentally observed in the brain. Ionic diffusion allows for short-term plasticity and STM, which form the basis of direction selectivity, RC, and other emerging cognitive computing concepts. While many of these phenomena have individually been demonstrated by proof of concept, their combination into full neural networks and their extension to alternative architectures, such as multiterminal devices and bottom-up nanostructures, may further develop this field of neuromorphic devices into a mature technology for manufacturable cognitive computing hardware.

#### ACKNOWLEDGMENTS

This work was supported by the Italian Ministry of Foreign Affairs and International Cooperation (Grant No. PGR01011) and by the MOST, China (Grant No. 2018YFE0118300).

#### DATA AVAILABILITY

Data sharing is not applicable to this article as no new data were created or analyzed in this study.

## REFERENCES

- <sup>1</sup>G. Indiveri and S.-C. Liu, Proc. IEEE **103**, 1379 (2015).

- <sup>2</sup>F. Rosenblatt, Report No. 85-460-1, Cornell Aeronautical Laboratory, 1957.

- <sup>3</sup>M. L. Minsky and S. A. Papert, *Perceptrons* (MIT Press, 2017).

- <sup>4</sup>Y. LeCun, Y. Bengio, and G. Hinton, Nature 521, 436 (2015).

D. S. Modha, Science **345**, 668 (2014). <sup>7</sup>G.-q. Bi and M.-m. Poo, J. Neurosci. **18**, 10464 (1998).

<sup>8</sup>J.-P. Pfister and W. Gerstner, J. Neurosci. **26**, 9673 (2006).

<sup>&</sup>lt;sup>5</sup>E. Chicca, F. Stefanini, C. Bartolozzi, and G. Indiveri, Proc. IEEE **102**, 1367 (2014).

<sup>&</sup>lt;sup>6</sup>P. A. Merolla, J. V. Arthur, R. Alvarez-Icaza, A. S. Cassidy, J. Sawada, F. Akopyan, B. L. Jackson, N. Imam, C. Guo, Y. Nakamura, B. Brezzo, I. Vo, S. K. Esser, R. Appuswamy, B. Taba, A. Amir, M. D. Flickner, W. P. Risk, R. Manohar, and