# Double Zinc Diffusion Optimization for Charge Persistence Reduction in InGaAs/InP SPADs

Fabio Telesca<sup>10</sup>, Fabio Signorelli<sup>10</sup>, and Alberto Tosi<sup>10</sup>, Member, IEEE

*Abstract*—We present an in-depth characterization of the impact of the double zinc diffusion 2D profile on the charge persistence effect in InGaAs/InP Single-Photon Avalanche Diodes (SPADs). Charge persistence might be mitigated by increasing the operating temperature, so as to reduce minority carriers' lifetime, as well as by increasing the number of grading layers. However, the first approach leads to higher dark count rate due to stronger thermal generation of dark carriers, while the latter is technologically challenging. We show that, by adjusting the depth and radius of the shallow zinc diffusion, the electric field profile in the InGaAs layer outside the active area can be optimized in order to effectively mitigate charge persistence, achieving also its complete suppression in specific structures. Our study is based on both TCAD simulations and experimental measurements of different SPADs, whose only difference is in the geometrical shallow diffusion parameters.

*Index Terms*—Charge persistence, InGaAs/InP, near-infrared detector, single-photon avalanche diode, single-photon avalanche diodes (SPAD), single photon detector, photon counting.

#### I. INTRODUCTION

T HE ability to detect single-photons in the near-infrared range has been gaining a lot of interest in the recent years, as it is the enabling technology for many applications, such as quantum communication [1], quantum cryptography [2] and quantum optics experiments [3], eye-safe light detection and ranging (LIDAR) [4] and near-infrared spectroscopy (NIRS) [5]. Given their advantages in terms of cost, size and ease of use,  $In_{0.53}Ga_{0.47}As/InP$  single-photon avalanche diodes (SPADs) are among the best near-infrared (NIR) single-photon detectors for such applications.

InGaAs/InP SPADs are usually operated in gated mode at low temperature (typically, <250 K), to reduce the primary noise contribution, i.e., thermal carrier generation in the In-GaAs region. However, lower temperature operation worsens afterpulsing probability (which ultimately limits the maximum photon count rate), as well as an often-overlooked phenomenon

Manuscript received 30 April 2023; revised 6 August 2023 and 10 November 2023; accepted 10 November 2023. Date of publication 15 November 2023; date of current version 2 January 2024. (*Corresponding author: Fabio Telesca.*)

Fabio Telesca and Alberto Tosi are with the Dipartimento di Elettronica, Informazione e Bioingegneria, Politecnico di Milano, 20133 Milano, Italy (e-mail: fabio.telesca@polimi.it; alberto.tosi@polimi.it).

Fabio Signorelli was with the Dipartimento di Elettronica Informazione e Bioingegneria, Politecnico di Milano, 20133 Milano, Italy. He is now with the Micro Photon Devices Srl, 39100 Bolzano, Italy (e-mail: fabio.signorelli@micro-photon-devices.com).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSTQE.2023.3332767.

Digital Object Identifier 10.1109/JSTQE.2023.3332767

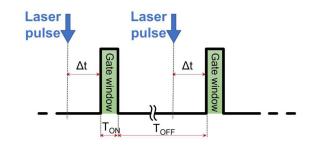

called *charge persistence*. Charge persistence is a source of noise originating from holes thermally- or photo-generated inside the InGaAs absorption layer at the periphery of the active area and that diffuse towards the central active area [6]. In gated mode operation, holes generated in the InGaAs layer are less likely to cross the hetero-barrier during the off time ( $T_{OFF}$ ), especially in the peripheral region outside the active area, since the lower electric field is linked to a lower tunneling probability. Therefore, a longer  $T_{OFF}$  leads to a larger number of holes accumulating at the hetero-interface: in the subsequent ON interval ( $T_{ON}$ , when the SPAD bias is beyond the breakdown level), some of the trapped holes may tunnel in correspondence of the active area (where the electric field is higher) and reach the multiplication region, thus igniting spurious avalanches.

Charge persistence is highly undesirable, and it cannot be exploited as a charge-focusing effect for extending the active area by collecting the photons absorbed outside the central active area, as it is based on the slow diffusion charge transport, thus leading to tails in the instrument response function that are in the nanosecond range. Moreover, charge persistence of thermallygenerated carriers adds up to DCR.

Such detrimental effect can be mitigated by either increasing the electric field at the heterointerface (with the drawback of increasing field-assisted carrier generation) or by incrementing the number of grading layers to facilitate tunneling even with a lower electric field (although increasing fabrication complexity).

In this article, we investigate the effects of charge persistence on the main performance metrics of an InGaAs/InP SPAD (photon detection efficiency – PDE, dark count rate – DCR, and instrument response function) and describe how it can be mitigated by tailoring the design of the double zinc diffusion 2D profile.

## II. DEVICE STRUCTURE

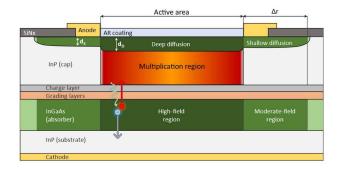

The devices under tests are InGaAs/InP SPADs designed at Politecnico di Milano, but different works described the charge persistence effect in other similar InGaAs/InP SPADs designed and fabricated by other groups [6], [7], [8]. Our front-illuminated SPADs have the typical separate absorption, grading, charge and multiplication (SAGCM) structure, as described in [9] and shown in Fig. 1. The SPAD active area is defined by p<sup>+</sup> doping the cap InP layer with a double zinc diffusion.

To assess the effect of the shape of the double zinc diffusion on charge persistence, we tested SPADs with 25  $\mu$ m active area diameter taken from two different wafers (which will be called wafer W1 and wafer W2 hereafter), grown in the same batch with

© 2023 The Authors. This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 License. For more information, see https://creativecommons.org/licenses/by-nc-nd/4.0/

Fig. 1. Schematic representation of an InGaAs/InP SPAD with the separate absorption, grading, charge and multiplication (SAGCM) structure. Layers and regions are labelled in the figure, as well as other features such as the difference between deep and shallow diffusion radius ( $\Delta$ r) and the schematic distribution of electric field in the InGaAs layer: High in the active area, moderate beneath the shallow diffusion and negligible elsewhere.

identical epitaxial structures and with the same deep diffusion depth (d<sub>D</sub>), but with wafer W2 having a shallow diffusion 100 nm deeper than that of wafer W1 (i.e.,  $d_{S2} = d_{S1} + 100$  nm). As a reference, this difference is less than 50% of d<sub>D</sub> - d<sub>S1</sub>. The two d<sub>S</sub> values were chosen after an extensive modeling and simulation work aimed at finding the upper limit of the shallow diffusion depth. A different d<sub>S</sub> is obtained by only varying the duration of the zinc diffusion process, while leaving all other process parameters unchanged. This assures that d<sub>S</sub> is the only dimension affected, while leaving the double zinc diffusion profile unaltered.

In a first comparison, we tested SPADs with a shallow diffusion radius 7  $\mu$ m larger than the deep diffusion radius, i.e.,  $\Delta r = 7 \mu$ m. Then, in order to further investigate the effect of the shallow diffusion radius on charge persistence, we also tested devices with  $\Delta r = 4 \mu$ m and  $\Delta r = 10 \mu$ m taken from wafer W2, whose devices show lower charge persistence.

## **III. TCAD SIMULATIONS**

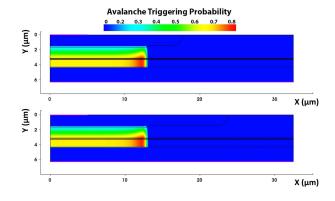

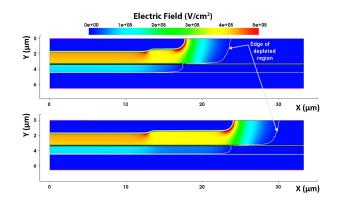

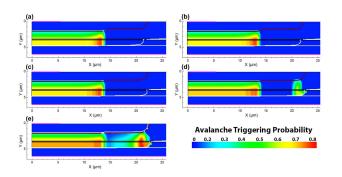

The main purpose of the shallow zinc diffusion is to limit premature edge breakdown, so that DCR is not increased. Moreover, the double zinc diffusion profile affects the uniformity of the bidimensional avalanche triggering probability across the active area: a uniform avalanche probability distribution positively impacts the instrument response function, PDE and noise. Using Synopsys Sentaurus [10] TCAD simulator, we determined that the minimum radius difference required to suppress premature edge breakdown is  $\Delta r = 4 \ \mu m$  at  $V_{EX} = 5 \ V$  (where  $V_{EX}$  is the excess bias voltage, i.e., the difference between the SPAD voltage and its breakdown level), which is the target excess bias value for these detectors. If the radius of the shallow diffusion is further increased, there are no significant changes in the avalanche triggering probability distribution (as an example, Fig. 2 shows simulation results for the wafer W2 SPADs with  $\Delta r = 4 \,\mu m$  and 10  $\mu m$ ). A similar observation can be made about the electric field: no major differences are visible in the active areas of the two devices. However, since the shallow diffusion of the SPAD with  $\Delta r = 10 \ \mu m$  spans over a much wider area, the depleted region extends more outside the active one,

Fig. 2. TCAD simulation of avalanche triggering probability at  $V_{EX} = 5 V$  at 225 K for W2 SPADs with  $\Delta r = 4 \mu m$  (top) and  $\Delta r = 10 \mu m$  (bottom), showing the probability that a free carrier generated anywhere in the device may ignite a self-sustaining avalanche. Increasing the shallow diffusion radius above  $4 \mu m$  has no further benefits in terms of active area confinement and uniformity.

Fig. 3. TCAD simulations of electric field at  $V_{\rm EX} = 5$  V at 225 K for W2 SPADs with  $\Delta r = 4 \ \mu m$  (top) and  $\Delta r = 10 \ \mu m$  (bottom). The white line indicates the edge of the depleted region. The avalanche triggering probability (shown in Fig. 2) does not depend on the local peaks of the electric field, but rather on the overall electric field experienced by carriers along their path to the collecting contact.

therefore the region around the active area where electric field is non-negligible is also increased (see Fig. 3).

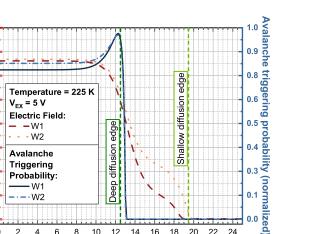

Regarding  $d_S$ , there are no substantial differences between wafers W1 and W2 in terms of the simulated avalanche triggering probability distribution, but the deeper shallow diffusion of wafer W2 leads to a higher electric field in the InGaAs layer beneath, as is shown in Fig. 4, which reports a mono-dimensional plot of both parameters for both wafers along a horizontal cut at the interface between the first grading layer and the InGaAs layer. According to simulations, the upper limit to  $d_S$  is roughly  $d_{S2} + 100$  nm: after that, the electric field below the shallow diffusion is so high that premature edge breakdown occurs below the shallow diffusion edge at  $V_{EX} = 5$  V, thus blunting the vertical confinement of the device active area and causing a detrimental effect on noise (see Fig. 5). As a conservative choice, we decided to fabricate SPADs with  $d_{S2}$  that is 100 nm below the upper limit.

Since there is no premature edge breakdown below the shallow diffusion of SPADs from wafer W2, we conclude that the higher electric field in the InGaAs layer of W2 is still below a value that would cause a DCR increase, but high enough to

1.0

0.9

0.8

0.6

0.5

0.4

0.3

0.1

0.0

0 2 4 6 8 10 12 14 16 18 20 22 24

Electric field (normalized)

Mono-dimensional plot of electric field (left Y axis) and avalanche Fig. 4. triggering probability (right Y axis) along a horizontal cut at the interface between the first grading layer and the InGaAs layer, obtained by simulating a SPAD with  $\Delta r = 7 \ \mu m$  for both wafers W1 and W2. The avalanche triggering probability distribution is roughly unchanged between the two wafers, but the electric field below the shallow diffusion is about double for W2 with respect to W1, due to the larger  $d_{S2}$ .

X (µm)

Fig. 5. Avalanche triggering probability with increasing depth of the shallow diffusion, from (a) to (e) (100 nm steps), at  $V_{\rm EX} = 5$  V. Wafers W1 and W2 are (b) and (c), respectively. Exact values are confidential.

enhance tunneling in correspondence of the shallow diffusion and thus reduce output pulses due to charge persistence.

## IV. EXPERIMENTAL CHARACTERIZATION

To experimentally characterize the impact of the double zinc diffusion profile on charge persistence and, subsequently, the main metrics of the SPAD, we performed measurements of PDE, DCR and instrument response function, at different temperatures and gating frequencies. For all the measurements here presented, the excess bias is  $V_{\rm EX}\,=\,5$  V, which is the target excess bias for these detectors, but we experimentally observed the same trends also at  $V_{\rm EX}$  = 3 V and  $V_{\rm EX}$  = 7 V: the charge persistence effect is much stronger at  $V_{\rm EX} = 3$  V, while it is weaker at  $V_{\rm EX} = 7$  V, as a consequence of the overall lower and higher electric field, respectively.

## A. Dark Count Rate vs. Gate Period

To measure DCR, the SPADs were placed in a vacuum chamber and cooled down to 225 K. A square wave was fed

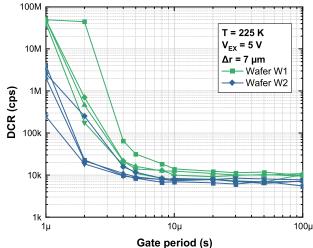

Fig. 6. Dependence of DCR on gate period for SPADs from wafers W1 and W2, both with  $\Delta r = 7 \ \mu m$ . The lower DCR of SPADs from W2 is traceable to a reduced impact of charge persistence thanks to the higher electric field beneath the shallow diffusion

to the cathode contact to drive the devices in gated mode, with a fixed ON time (i.e.,  $T_{ON} = 50$  ns) while continuously varying the gating period, so that  $T_{OFF}$  would vary as  $T_{OFF}$  = Gate period -  $T_{\rm ON}$ . The device was DC biased 0.5 V below breakdown and the amplitude of the square wave was set to 5.5 V, so to have  $V_{\rm EX} = 5 V.$

For SPADs with  $\Delta r = 7 \,\mu m$ , results are shown in Fig. 6. The SPADs taken from W1 typically have a higher DCR with respect to those from W2 (10 kcps vs. 7 kcps). Given the almost identical avalanche triggering probability profile in the active area, we ruled out the possibility that the higher DCR of wafer W1 could be due to a higher tunneling generation in correspondence of the deep diffusion edge. On the other hand, the higher electric field beneath the shallow diffusion of W2 may be linked to a higher tunneling probability through the hetero-barrier of holes that, being thermally generated in the InGaAs layer, are sunk by the anode contact without crossing the multiplication region and, thus, not igniting an avalanche.

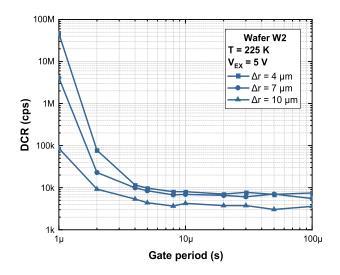

For shorter periods, DCR is dominated by afterpulsing, which causes a steep increase in the curve. Fig. 7 shows DCR measurements on SPADs with  $\Delta r = 4 \,\mu m$ , 7  $\mu m$ , and 10  $\mu m$  taken from wafer W2: the wider shallow diffusion is linked to lower DCR because the depleted region is wider and, consequently, holes have a higher probability of crossing the hetero-barrier without reaching the central active region.

#### B. Photon Detection Efficiency at 1550 nm

The photon detection efficiency maps at 1550 nm of SPADs from both wafers were measured by using a fiber-coupled CW laser and a calibrated photodiode to monitor the optical power. All devices were tested in the same operating conditions: cooled down to 225 K in a vacuum chamber and operated in gated mode with  $V_{EX} = 5 \text{ V}$ ,  $T_{ON} = 50 \text{ ns}$  and  $T_{OFF} = 50 \mu \text{s}$  (which is long enough to rule-out afterpulsing). The vacuum chamber was placed on three micro-positioning axes that allowed to move it

Fig. 7. Dependence of DCR on the gate period for SPADs with increasing  $\Delta r$  taken from wafer W2. The DCR decrease with a wider shallow diffusion further confirms the dependence of DCR on the electric field distribution below the shallow diffusion.

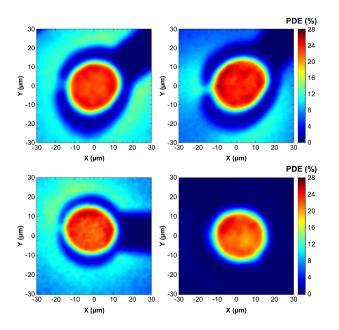

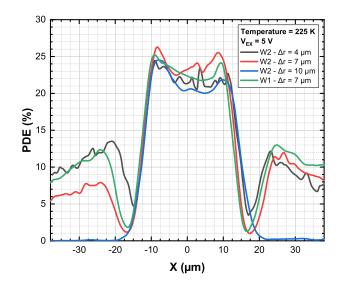

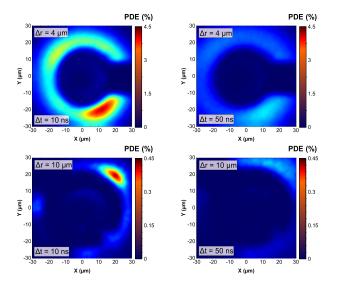

Fig. 8. PDE maps at  $V_{\rm EX} = 5$  V and T = 225 K, for SPADs with  $\Delta r = 7 \,\mu m$  taken from wafers W1 (top left) and W2 (top right), and for SPADs from wafer W2 with  $\Delta r = 4 \,\mu m$  (bottom left) and  $\Delta r = 10 \,\mu m$  (bottom right), measured with a 1550 nm CW laser. The probability of detecting photons absorbed outside the active area decreases (i.e., photogenerated carriers cross the hetero-barrier before reaching the active area) as the shallow diffusion is made deeper and wider.

with 500 nm steps. The laser was focused on the SPAD with a collimator and a single lens in a  $\sim 5 \,\mu$ m spot, and the whole chip area was scanned by moving the chamber in the XY directions. Results are shown in Fig. 8.

For SPADs with the  $\Delta r = 7 \mu m$  from wafer W1 and W2, the PDE in the active area is similar, with an average value of 24% and local peaks of ~27% (first row in Fig. 8). For both SPADs, the probability of detecting a photon when the laser spot was focused outside the SPAD area is in the order of 10%, visible in

Fig. 9. PDE along diagonal cuts passing through the device center of the maps shown in Fig. 8.

the maps as a non-uniform cyan hue surrounding the device. The dark blue circle and diagonal segment are due to the shadows of the anode metals. Minor image distortions that are visible in some of the measurements are due to artifacts introduced by the motorized axes.

The main difference between the two wafers is that for wafer W1 the probability of detecting a photon absorbed outside the SPAD area is higher with respect to wafer W2, as can be also seen in the mono-dimensional plots along diagonal cuts shown in Fig. 9 (green and red curve, respectively). This shows that charge persistence is indeed stronger in wafer W1 than in wafer W2 and, given that the only difference between the two is  $d_s$ , conclusions of Section III-A are confirmed.

Regarding SPADs with  $\Delta r = 4 \ \mu m$  and 10  $\mu m$  from wafer W2, PDE in the active area is still similar for both devices (~23%), as shown in Figs. 8 and 9.

In the case of the  $\Delta r = 4 \ \mu m$  SPAD, PDE outside the active area is in the order of 10% up to ~35  $\mu m$  away from the SPAD center. This shows that the effect of charge persistence is dominant, due to the small shallow diffusion diameter. On the other hand, PDE outside the SPAD area is greatly reduced when  $\Delta r = 10 \ \mu m$ , meaning that the wider shallow diffusion and, consequently, wider depleted region in the InGaAs layer, mitigates charge persistence.

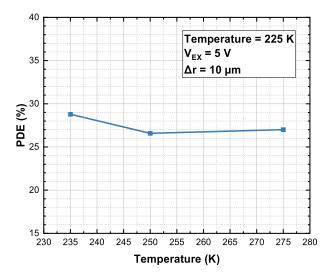

We also measured the PDE of the SPAD with  $\Delta r = 10 \ \mu m$ by illuminating the whole die area with 1550 nm wavelength photons, at different temperatures. The PDE maps showed that the actual SPAD opening diameter is 27  $\mu m$  rather than the nominal 25  $\mu m$ , due to the fact that the metal opening is 2  $\mu m$ wider than the deep diffusion mask, therefore the photon-sensing area was considered to be a 27  $\mu m$  diameter circle. The PDE was measured by operating the SPAD in gated mode with a fixed V<sub>EX</sub> = 5 V and changing the bias so that it was always 0.5 V below breakdown at each temperature. We found a PDE of ~26% at both 275 K and 250 K, while it increased to 29% at 235 K (see Fig. 11). It is known that, if the excess bias is

Fig. 10. PDE maps built by scanning a pulsed 1550 nm laser focused on the SPAD area at  $\Delta t = 10$  ns (left column) and  $\Delta t = 50$  ns (right column) before the gate window for SPADs from wafer W2 with  $\Delta r = 4 \mu m$  (top row) and  $10 \mu m$  (bottom row). As  $\Delta r$  is increased, charge persistence is reduced, therefore photons absorbed before the gate window are less likely to be detected.

Fig. 11. PDE at 1550 nm estimated by flood-illuminating the SPAD with  $\Delta r = 10 \ \mu m$  from wafer W2. For temperatures below 20 K, charge persistence distorts PDE estimation.

kept constant (5 V in our measurements), the PDE at lower temperatures is higher, due to the decrease of the breakdown voltage with temperature which leads to the excess bias being a larger share of the total applied voltage. However, the reported increase in PDE is present only for low temperatures and it is too sharp to be ascribed to such effect. Moreover, it was not possible to perform a PDE measurement at 225 K: if we keep assuming the SPAD active area to be a 27  $\mu$ m diameter circle, the measured PDE at 225 K was higher than 100%, which is meaningless. Our conclusion is that, at lower temperatures, the actual area where absorbed photons are detected is much wider than the nominal one due to charge persistence and, at 225 K, even for the SPAD with  $\Delta r = 10 \ \mu$ m, although charge persistence is not dominant

Fig. 12. Scheme for PDE measurements with a laser pulse reaching the device before the gate window.

according to the measurements shown in Fig. 8, it is still too high to estimate PDE by flood-illuminating the detector.

On the other hand, for the SPAD with  $\Delta r = 4 \ \mu m$  it was not possible to measure PDE with flood-illumination at any temperature, since the effect of charge persistence is always dominant.

## C. PDE Maps With Pulsed Laser Before Gate Window

To better quantify the intensity of charge persistence in the SPADs from wafer W2, we acquired additional PDE maps, but with a pulsed 1550 nm laser focused on the SPAD chip surface and arriving at a given  $\Delta t$  time before the gate window, as exemplified by the scheme in Fig. 12. With such approach, we could estimate the percentage of photons absorbed outside the SPAD generating carriers that do not recombine before reaching the multiplication region. The measurements were performed at 225 K, with  $V_{\rm EX} = 5$  V.

Measurement results are shown in Fig. 10: the probability to detect a photon from a circular area up to 10  $\mu$ m away for the SPAD with  $\Delta r = 4 \mu$ m is in the order of 3% with  $\Delta t = 10$  ns, and it is still around 1% with  $\Delta t = 50$  ns. We also noticed that the events resulting from charge persistence are often unevenly distributed in space, probably because they are closely related to local peaks in the electric field, which may depend on defects in the device. The maps in Fig. 10 suggest that most of the charge persistence effect is ascribable to carriers absorbed just before the gate window, but some events are still detected with  $\Delta t = 50$  ns. On the other hand, for the SPAD with  $\Delta r = 10 \mu$ m, these probabilities drop by an order of magnitude, which is in line with what was shown in the bottom row of Fig. 8.

## D. Instrument Response Function

Finally, the instrument response function of SPADs from wafer W2 was measured illuminating the whole die area with a 1550 nm pulsed laser.

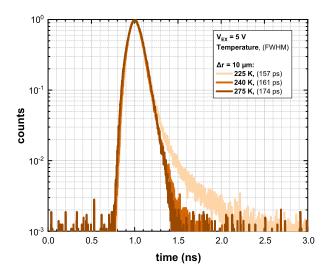

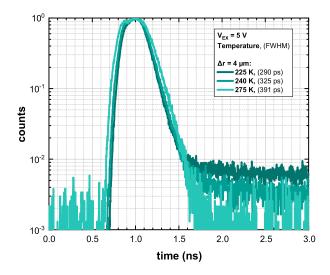

The SPAD with  $\Delta r = 10 \ \mu m$  has a timing jitter (measured as full-width at half-maximum – FWHM – of the instrument response function) of 157 ps at 225 K, which increases slightly with temperature, up to 174 ps at 275 K (see Fig. 13). For the SPAD with  $\Delta r = 4 \ \mu m$ , a FWHM of 290 ps was measured at 225 K, and it raised to 391 ps at 275 K (see Fig. 14). Most of the increase of FWHM is due to the higher number of scattering phenomena occurring at higher temperature. Besides such

Fig. 13. Instrument response function of SPADs from wafer W2 with  $\Delta r = 10 \ \mu m$  at different temperatures. The exponential tail after the main peak is related to charge persistence.

Fig. 14. Instrument response function of SPADs from wafer W2 with  $\Delta r = 4 \,\mu m$  at different temperatures. The diffusion tail due to charge persistence is much more prominent than that of SPADs with  $\Delta r = 10 \,\mu m$ , even at higher temperatures.

FWHM variation, the main difference between the two devices is in the diffusion tail of the instrument response function: the SPAD with  $\Delta r = 4 \,\mu m$  shows a marked tail at 225 K, with a time constant in the order of several nanoseconds, which gradually decreases as the temperature rises. Such trend indicates that the tail is due to the slow diffusing carriers that give rise to charge persistence: at higher temperatures, the minority carrier lifetime swiftly decreases, leading to the reduction of the tail. Similarly, the instrument response function of the SPAD with  $\Delta r = 10 \,\mu m$  also has a tail at low temperature, although much less pronounced, meaning that charge persistence is much less important for this device, but still present. Additionally, such tail disappears at temperature above 240 K. These results confirm that it was possible to measure PDE for the SPAD with  $\Delta r = 10$   $\mu m$  for temperature above 250 K, while this was not the case for the other detector.

### V. CONCLUSION

We characterized the dependence of charge persistence on shape and depth of the shallow zinc diffusion in InGaAs/InP SPADs operated in different conditions, by investigating how it affects the main parameters of a SPAD: DCR, PDE and instrument response function.

Specifically, we observed that charge persistence can be mitigated by designing a deeper and wider shallow diffusion, since both design choices result in a higher electric field in the InGaAs layer around the active area, thus increasing tunneling probability of holes diffusing from the surrounding region, allowing to drain them towards the anode before they reach the central active area, where they would trigger avalanches.

We conclude that, even without modifying the epitaxial structure of the device, charge persistence can be reduced with a design targeted for operating the detector at higher temperatures (namely, above 250 K) and with higher electric field in the absorption layer.

#### REFERENCES

- N. Gisin and R. Thew, "Quantum communication," *Nature Photon.*, vol. 1, no. 3, pp. 165–171, Mar. 2007.

- [2] I. P. Vaisband et al., On-Chip Power Delivery and Management, 4th ed. Berlin, Germany: Springer-Verlag, 2016.

- [3] M. Davanço et al., "Telecommunications-band heralded single photons from a silicon nanophotonic chip," *Appl. Phys. Lett.*, vol. 100, no. 26, Jun. 2012, Art. no. 261104.

- [4] Y. U. Chao et al., "Fully integrated free-running InGaAs/InP single-photon detector for accurate lidar applications," *Opt. Exp.*, vol. 25, no. 13, pp. 14611–14620, Jun. 2017.

- [5] S. A. Carp et al., "Diffuse correlation spectroscopy measurements of blood flow using 1064 nm light," *J. Biomed. Opt.*, vol. 25, no. 09, Sep. 2020, Art. no. 97003.

- [6] N. Calandri, M. Sanzaro, A. Tosi, and F. Zappa, "Charge persistence in InGaAs/InP single-photon avalanche diodes," *IEEE J. Quantum Electron.*, vol. 52, no. 3, Mar. 2016, Art. no. 4500107, doi: 10.1109/JQE.2016.2526608.

- [7] Y. S. Lee, K. Y. Chen, S. Y. Chien, and S. C. Chang, "Characteristics of charge persistence in InGaAs/InP single-photon avalanche diode," *IEEE Photon. Technol. Lett.*, vol. 30, no. 22, pp. 1980–1982, Nov. 2018, doi: 10.1109/LPT.2018.2874041.

- [8] J. Zhang, R. Thew, J.-D. Gautier, N. Gisin, and H. Zbinden, "Comprehensive characterization of InGaAs–InP avalanche photodiodes at 1550 nm with an active quenching ASIC," *IEEE J. Quantum Electron.*, vol. 45, no. 7, pp. 792–799, Jul. 2009, doi: 10.1109/JQE.2009.2013210.

- [9] F. Signorelli et al., "Low-noise InGaAs/InP single-photon avalanche diodes for fiber-based and free-space applications," *IEEE J. Sel. Topics Quantum Electron.*, vol. 28, no. 2, Mar./Apr. 2022, Art. no. 3801310, doi: 10.1109/JSTQE.2021.3104962.

- [10] "TCAD Sentaurus R-2020.09," Synopsys, 2020.

Fabio Telesca was born in Melfi, Italy, in 1994. He received the bachelor's degree (*cum laude*) in biomedical engineering and the master's degree (*cum laude*) in electronics engineering in 2017 and 2020 respectively, from Politecnico di Milano, Milan, Italy, where he has been working toward the Ph.D. degree in information technology since 2020. His research interests include the characterization and design of InGaAs/InP single-photon avalanche diodes for near-infrared applications.

Fabio Signorelli was born in Bergamo, Italy, in 1994. He received the M.Sc. degree in electronics engineering and the Ph.D. degree (*cum laude*) in information technology from Politecnico di Milano, Milan, Italy, in 2018 and 2022, respectively. He is currently an R&D Device Engineer with Micro Photon Devices Srl, Bolzano, Italy. His research interests include the design, development, and characterization of visible and near-infrared single-photon avalanche diodes (SPADs) and SPAD arrays in Silicon, Germanium and InGaAs/InP semiconductors.

Alberto Tosi (Member, IEEE) was born in Borgomanero, Italy, in 1975. He received the master's degree in electronics engineering and the Ph.D. degree in information technology engineering from the Politecnico di Milano, Milan, Italy, in 2001 and 2005, respectively. From 2006 to 2014, he was an Assistant Professor Since 2014, he has been an Associate Professor of electronics with the Politecnico di Milano. In 2004, he was a Student with the IBM T. J. Watson Research Center, Yorktown Heights, NY, USA, working on optical testing of CMOS circuits.

He currently works on silicon and InGaAs/InP single-photon avalanche diodes (SPADs). His research interests include the arrays of silicon SPADs for 2-D and 3-D applications and time-correlated single-photon counting electronics.